# 2001 1K (128 x 8) Non-Volatile Random Access Memory

- 5 Volt Only Operation

- Fast Static RAM Read Access Time 2001-2, 180 ns Max. 2001. 300 ns Max.

- Single Line STORE & RECALL

- 10 ms Self-Timed STORE Cycle

- Automatic Recall on Power Up

- Write Protect Circuit to Preserve Data On Power-Up and Power-Down

- Multiplexed Address and Data Bus

- **Lower Power Standby Mode**

- 10-Year Data Retention for each STORE

- Minimum 10,000 Non-Volatile STORE Cycle Endurance

- Unlimited Endurance for Read, Write and RECALL Cycles

- HMOS\*-E FLOTOX Cell Design

- Available in 18-Lead Cerdip and Plastic Packages

(See Packaging Spec. Order #231369)

The Intel 2001 Non-Volatile Random Access Memory (NVRAM) is a 1K device organized 128 x 8. It provides the real-time read/write functions of a static RAM together with the reliable non-volatile storage capability of an E²PROM array to preserve its memory contents when power is removed. The multiplexed address and data bus allows the 2001 to interface directly to the iAPX 88 and iAPX 188 microprocessors and MCS®-51 microcomputer to provide a maximum level of system integration.

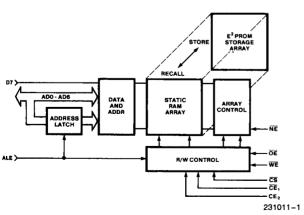

Internally, the 2001 NVRAM consists of a high speed static RAM array backed up, bit-for-bit, by an E<sup>2</sup>PROM array for non-volatile storage. The transfer of memory data between the static RAM and the E<sup>2</sup>PROM array occurs in parallel for fast storage and recall as well as minimal system support.

Two functions are provided to transfer data between the volatile RAM and its non-volatile  $E^2PROM$  counterpart. The STORE function transfers RAM data into the  $E^2PROM$  while the RECALL function fetches  $E^2PROM$  data and places it in the RAM array. Both functions are controlled by a single  $\overline{NE}$  signal which can easily be activated with traditional circuitry in memory mapped space, through an I/O port, or from the output of a power-fail detector.

The RAM operating characteristics of the 2001 NVRAM provides high speed microprocessor performance with unlimited endurance. In the non-volatile storage mode, data retention is specified at over 10 years for each STORE operation. Over 10,000 STORE operations can be performed reliably.

The 2001 NVRAM is furnished in an 18-pin, 300 mil package with its address and data lines multiplexed for direct interface to specific microcontrollers and microprocessors.

\*HMOS is a patented process of Intel Corporation.

Figure 1. 2001 Functional Diagram

| AD0-AD6         | Multiplexed Address/Data Lines                |

|-----------------|-----------------------------------------------|

| D7              | Data Bit 7                                    |

| WE              | Write Enable                                  |

| ŌĒ              | Output Enable                                 |

| <u>cs</u>       | Chip Select                                   |

| CE <sub>1</sub> | Chip Enable 1                                 |

| CE <sub>2</sub> | Chip Enable 2                                 |

| NE              | Non-Volatile Enable<br>(Store/Recall Control) |

| ALÉ             | Address Latch Enable                          |

| NC              | No Internal Connection                        |

2001 Pin Names

| AD <sub>0</sub>   AD <sub>1</sub>   AD <sub>2</sub>   AD <sub>4</sub>   AD <sub>6</sub>   AD <sub>6</sub> | 9<br>4 2001 | 16 V <sub>C</sub> 17 OE 16 WE 19 AL 14 CE 12 CE 12 CE | E<br>E   |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------|----------|--|

| AD, [                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •           |                                                       | -        |  |

| D, 🗖                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |                                                       |          |  |

| V80 🖂                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •           | NC                                                    | 231011-2 |  |

Figure 2. 2001 Pin Configuration

### **DEVICE OPERATION**

The design of the 2001 NVRAM allows it to be connected directly to the multiplexed address/data bus of the iAPX 88 and iAPX 188 microprocessors, and the MCS-51 microcontroller. The 7 address lines and lower 7 data bits for the 2001 are multiplexed on pins AD0-AD6. The falling edge of ALE (Address Latch Enable) strobes the seven address bits of AD0-AD6 and the states of  $\overline{\text{CE}}_1$  and  $\text{CE}_2$  into the 2001's on-chip latches. The rising edge of  $\overline{\text{WE}}$  writes the data from the address/data bus into the RAM array location specified by the latched address. An ALE pulse is required for STORE and RECALL initiation cycles as well as read and write cycles. The 2001's operational modes are given in Table 1.

Table 1. 2001 Operational Modes V<sub>CC</sub> = 5V

| Mode Pin                                        | CE <sub>1</sub> | CE <sub>2</sub> | ĊS              | OE              | WE       | NE       | Data     |

|-------------------------------------------------|-----------------|-----------------|-----------------|-----------------|----------|----------|----------|

| Standby                                         | $V_{IH}$        | Х               | х               | х               | Х        | Х        | Hi-Z     |

|                                                 | Х               | V <sub>IL</sub> | х               | Х               | х        | Х        | Hi-Z     |

| Read                                            | VIL             | VIH             | ViL             | VIL             | VIH      | VIH      | Data Out |

| Write                                           | VIL             | $V_{\text{IH}}$ | V <sub>IL</sub> | $V_{\text{IH}}$ | VIL      | VIH      | Data In  |

| Automatic RECALL<br>at V <sub>CC</sub> Power Up | х               | х               | х               | Х               | x        | х        | Hi-Z     |

| Normal RECALL                                   | V <sub>IL</sub> | $V_{IH}$        | $V_{IL}$        | $V_{IL}$        | VIH      | VIL      | Hi-Z     |

| STORE                                           | $V_{IL}$        | V <sub>IH</sub> | $V_{IL}$        | VΙΗ             | $V_{IL}$ | $V_{IL}$ | Hi-Z     |

### NOTES:

1. X = Don't Care.

2. The  $\overline{\text{CE}}_1$  and  $\text{CE}_2$  inputs are latched by the falling edge of ALE for Read and Write cycles. For STORE and RECALL initiation cycles, ALE may be either pulsed as in Write and Read cycles (see Write and Read cycles timing diagrams) or ALE can be held at  $V_{IH}$  for the active duration of  $\overline{\text{CS}}$ . In the latter case  $\overline{\text{CE}}_1$  and  $\text{CE}_2$  should also be held active for as long as  $\overline{\text{CS}} = V_{II}$ .

Reading or writing to the 2001's RAM array allows immediate random access to any of the 128 bytes in that array. To do a read or write cycle, a  $V_{IL}$  level is put on the  $\overline{CS}$  pin and a  $V_{IH}$  level on the  $\overline{NE}$  pin. A read cycle is performed by putting a  $V_{IL}$  level on  $\overline{OE}$  with  $\overline{WE}$  held high, and a write cycle is performed by applying a  $V_{IL}$  level to  $\overline{WE}$  with  $\overline{OE}$  held high.

The timing for a RECALL or a STORE initiation cycle is the same as for a read or write cycle, respectively, except that a  $V_{IL}$  level is applied to the  $\overline{NE}$  input.

### **RECALL OPERATION**

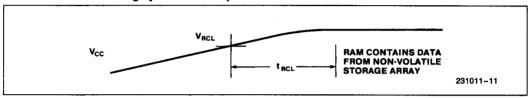

A RECALL operation is initiated by bringing  $\overline{OE}$  low while  $\overline{NE} = V_{IL}$ . This causes the data from the NVRAM's internal non-volatile storage array to be transferred to the static RAM array, from which it can be externally accessed. The RECALL function

can be activated by the CPU at any time, as often as desired without affecting the integrity of the data in the non-volatile storage array. The RECALL function occurs automatically when V<sub>CC</sub> is applied.

### STORE

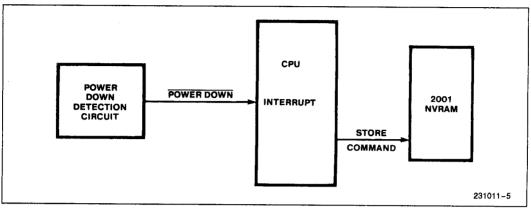

A STORE operation is started by bringing  $\overline{\text{WE}}$  low with  $\overline{\text{NE}}=\text{V}_{\text{IL}}$ . This causes the data in the static RAM array to be transferred to the non-volatile storage array. The STORE function is typically used to save data at system power-down and is initiated when a POWER DOWN signal is received by the system from the power supply or a power supply monitoring circuit. Since the STORE cycle takes 10 ms for reliable storage, the NVRAM's V<sub>CC</sub> supply must be maintained at no less than V<sub>CC</sub> Min for at least 10 ms. (V<sub>CCMIN</sub>=4.75V for parts with 5% V<sub>CC</sub> tolerance.)

### TWO-LINE CONTROL

The 2001 Non-Volatile RAM features 2-line control. By requiring a Chip Select ( $\overline{CS} = V_{IL}$ ) whenever a device function is to be activated (determined by  $\overline{OE}$ ,  $\overline{WE}$ , and  $\overline{NE}$ ), data bus contention is eliminated, system noise is reduced, and system design is simplified.

## MULTIPLE CHIP SELECTS ALLOWS MEMORY DECODING

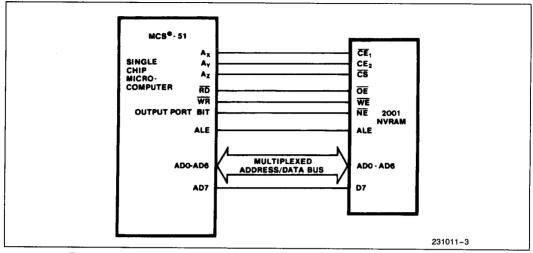

The 2001 has three device enabling control inputs,  $\overline{\text{CS}}$ ,  $\overline{\text{CE}}_1$ , and  $\text{CE}_2$ . Having multiple device enable lines allows memory decoding to be done by connecting the enable lines to system addresses. In the MCS-51 microcontroller example in Figure 3, by connecting  $\overline{\text{CS}}$ ,  $\overline{\text{CE}}_1$ , and  $\text{CE}_2$  to addresses A13, A14, and A15, respectively, the 2001 would be memorymapped at location 8000H.

### STANDBY MODE

Power for the internal circuitry of the 2001 NVRAM is controlled by the  $\overline{CE}_1$  and  $CE_2$  inputs. When either input is inactive ( $\overline{CE}_1 = V_{IH}$  or  $CE_2 = V_{IL}$ ), the NVRAM is in the Standby mode and consumes 65% less power. In this mode the address/data pins are in a high impedance state.

### STORE AND RECALL CONSIDERATIONS

Data retention for data that has been written into the 2001's non-volatile array by a STORE operation is greater than 10 years. The STORE endurance is a minimum of 10<sup>4</sup> cycles, that is, at least 10,000 STORE operations can be reliably performed.

Figure 3. Using the 2001 NVRAM with an MCS®-51 Single Chip Microcomputer

#### NOTE:

$A_X$ ,  $A_Y$ , and  $A_Z$  are any three of the MCS®-51 address pins A8-A15. By connecting  $\overline{CE}_1$ ,  $CE_2$ , and  $\overline{CS}$  to specific address lines, the 2001 can be mapped to a particular range in memory, eliminating the need for an external memory decoder.

# ON-CHIP DATA PROTECTION DURING SYSTEM POWER UP/DOWN

The 2001 NVRAM has an on-chip STORE lockout circuit which prevents spurious STOREs from occurring when system power is being applied or taken away. This on-chip circuit frees the designer from having to design in an external data protection circuit.

Spurious STOREs can be caused by unstable system control signals generated by system components when  $V_{CC}$  is rising or falling during system power up or power down. Although a STORE operation is normally initiated in an NVRAM when system power-down is detected, a second spurious STORE caused by unpredictable system components due to falling power could cause incorrect data to be transferred to the non-volatile storage array.

The on-chip STORE lockout circuit prevents a STORE operation from being initiated when  $V_{CC}$  is below 4V ( $V_{LKO}$ ). Since systems tend to stabilize when  $V_{CC}$  is above 3.5V, this value provides suitable margin. For more information about power up/down data protection, see Application Note AP-165.

### SYSTEM IMPLEMENTATION

The multiplexed address/data bus of the 2001 allows the device to be directly connected to the address/data bus of microprocessors such as the

iAPX 88 and the iAPX 188, and to microcomputers such as the MCS-51. Figure 3 shows an example of a 2001 connected to an MCS-51 microcomputer. The  $\overline{\text{NE}}$  signal is generated by one of the MCS-51's I/O output port bits. The three enable signals on the 2001,  $\overline{\text{CE}}_1$ ,  $\text{CE}_2$ , and  $\overline{\text{CS}}$  are connected directly to specific address bits that map the device into a particular address range, thus eliminating the need for a memory decoder.

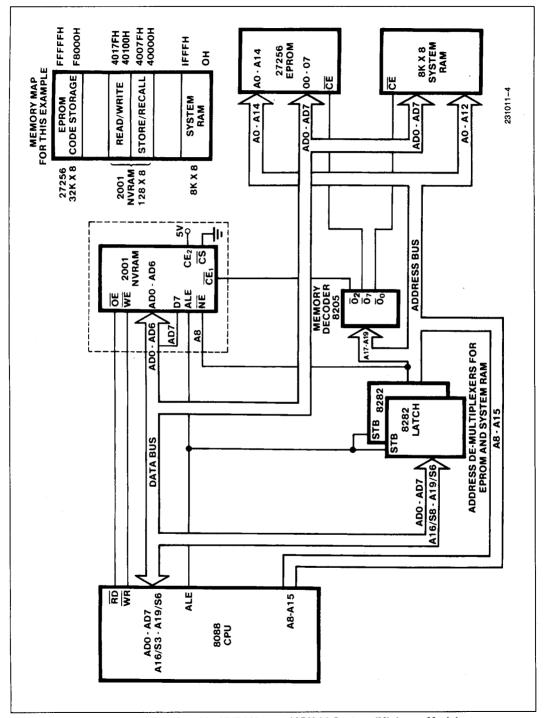

Figure 4 shows the 2001 in an iAPX 88 minimum mode system. As in the MCS-51 system in Figure 3, no additional system components are needed for the 2001. The 2001's address/data bus connects directly to AD0-AD6 of the iAPX 88, and system address line A8 is used to drive the NE input. As shown in the memory map for this example in Figure 4, Store/Recall access is done at addresses 40000H-40007FH, and a write or a read cycle at address 40100H will start a WRITE or a READ operation, respectively.

The 2001 NVRAM is typically used in a system to save critical data when the system powers down. This is done by connecting a POWER DOWN signal to an interrupt input on the CPU such that an interrupt subroutine is called when system power starts to fall. The interrupt subroutine writes all critical system data to the NVRAM's RAM array, then initiates a STORE operation. The STORE operation transfers the on-chip RAM array data to the device's non-volatile storage array. (See Figure 5.)

Figure 4. Adding the 2001 NVRAM to an iAPX 88 System (Minimum Mode)

Figure 5. Basic NVRAM System Implementation

### **ABSOLUTE MAXIMUM RATINGS\***

Temperature Under Bias . . . . .  $-10^{\circ}$ C to  $+80^{\circ}$ C Storage Temperature . . . .  $-65^{\circ}$ C to  $+125^{\circ}$ C All Input or Output Voltages with Respect to Ground . . . . . +6V to -0.3V

\*Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### D.C. CHARACTERISTICS

Operating Conditions:  $T_A = 0$ °C to +70°C,  $V_{CC} = 5V \pm 5$ %

| Symbol           | Parameter                                                                                 | 20      | 01-2               | 2       | 001                | Units | Conditions                                                                          |

|------------------|-------------------------------------------------------------------------------------------|---------|--------------------|---------|--------------------|-------|-------------------------------------------------------------------------------------|

|                  | 7                                                                                         | Min     | Max                | Min     | Max                | Units | Conditions                                                                          |

| lu               | Input leakage current                                                                     |         | 10                 |         | 10                 | μΑ    | V <sub>CC</sub> = Max,<br>V <sub>IN</sub> = GND to V <sub>CC</sub>                  |

| lo               | Output leakage current                                                                    |         | 10                 |         | 10                 | μΑ    | V <sub>CC</sub> = Max,<br>V <sub>OUT</sub> = GND to V <sub>CC</sub>                 |

| lcc1             | V <sub>CC</sub> current (Standby)                                                         |         | 35                 |         | 30                 | mA    | V <sub>CC</sub> = Max,<br>CE = V <sub>IH</sub> or CE <sub>2</sub> = V <sub>IL</sub> |

| ICC2             | V <sub>CC</sub> current (Active)                                                          |         | 100                |         | 85                 | mA    | V <sub>CC</sub> = Max,<br>Mode = Read or Write                                      |

| Іссз             | V <sub>CC</sub> current (STORE)                                                           |         | 100                |         | 85                 | mA    | V <sub>CC</sub> =Max,<br>Mode=STORE                                                 |

| ICC4             | V <sub>CC</sub> current (RECALL)                                                          | ,       | 100                |         | 85                 | mA    | V <sub>CC</sub> = Max,<br>Mode = RECALL                                             |

| VIL              | Input low voltage                                                                         | -0.1(1) | 0.8                | -0.1(1) | 0.8                | ٧     |                                                                                     |

| V <sub>IH</sub>  | Input high voltage                                                                        | 2.0     | V <sub>CC</sub> +1 | 2.0     | V <sub>CC</sub> +1 | V     |                                                                                     |

| VoL              | Output low voltage                                                                        |         | 0.4                |         | 0.4                | V     | I <sub>OL</sub> = 2.1 mA                                                            |

| V <sub>OH</sub>  | Output high voltage                                                                       | 2.4     |                    | 2.4     |                    | V     | I <sub>OH</sub> = -400 μA                                                           |

| V <sub>RCL</sub> | V <sub>CC</sub> level at which automatic<br>RECALL begins during V <sub>CC</sub> Power-Up | 4.0     |                    | 4.0     |                    | V     | <u> </u>                                                                            |

| $V_{LKO}$        | V <sub>CC</sub> level for STORE lockout                                                   | 4.0     | 4.65               | 4.0     | 4.65               | v     |                                                                                     |

NOTE:

<sup>1. -1.0</sup>V spikes less than 20 ns in duration are allowed.

### **CAPACITANCE** (T<sub>A</sub> = 25°C, f = 1 MHz)

| Symbol           | Parameter          | Typ.(1) | Max | Units | Test Conditions                                                                             |

|------------------|--------------------|---------|-----|-------|---------------------------------------------------------------------------------------------|

| C <sub>IN</sub>  | Input Capacitance  | 5       | 10  | pF    | V <sub>IN</sub> =OV                                                                         |

| C <sub>OUT</sub> | Output Capacitance |         | 10  | рF    | $\overrightarrow{OE} = \overrightarrow{CE}_1 = \overrightarrow{CS} = V_{IH}, CE_2 = V_{IL}$ |

### A.C. TEST CONDITIONS

$\label{eq:continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous_continuous$

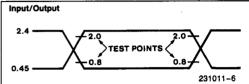

### A.C. Testing Input, Output Waveform

A.C. Testing inputs are driven at 2.4V for a Logic 1 and 0.45V for a Logic 0. Timing measurements are made at 2.0V for a Logic 1 and 0.8V for a Logic 0.

### A.C. CHARACTERISTICS

### **Read Cycle**

| Cumbal              | Parameter                                                       | 2001-2 |     | 20  | Units |         |

|---------------------|-----------------------------------------------------------------|--------|-----|-----|-------|---------|

| Symbol              | , Fai ailleter                                                  | Min    | Max | Min | Max   | J.III.G |

| t <sub>LD</sub>     | ALE to Valid Data Out<br>(Access Time)                          |        | 180 |     | 300   | ns      |

| t <sub>OE</sub>     | OE Access Time                                                  |        | 120 |     | 170   | ns      |

| t <sub>RP</sub>     | OE Pulse Width                                                  | 150    |     | 250 |       | ns      |

| tон                 | Output Held from Addresses, CS, or OE (whichever changes first) | 0      |     | 0   |       | ns      |

| t <sub>DF</sub> (1) | OE High to Output Not Driven                                    | 0      | 60  | 0   | 95    | ns      |

| toLZ                | OE Low to Output Driven                                         | 10     |     | 10  |       | ns      |

### **Write Cycle**

| Cumbal          | Parameter                     | 200 | 01-2 | 20  | Units |       |

|-----------------|-------------------------------|-----|------|-----|-------|-------|

| Symbol          | Parameter                     | Min | Max  | Min | Max   | Onito |

| twp             | Write Pulse Width             | 150 |      | 250 |       | ns    |

| t <sub>DS</sub> | Data Valid to End of Write    | 150 |      | 150 |       | ns    |

| t <sub>DH</sub> | Data Valid After End of Write | 15  |      | 20  |       | ns    |

NOTE:

<sup>1.</sup> This parameter only sampled and not 100% tested.

Timing For ALE,  $\overline{\text{CE}}_1$ ,  $\text{CE}_2$ , and  $\overline{\text{CS}}$

| Symbol            | Parameter                        | 2001-2 |     | 2001 |     | Units |

|-------------------|----------------------------------|--------|-----|------|-----|-------|

|                   | r utullioto)                     | Min    | Max | Min  | Max | J     |

| t <sub>LL</sub>   | ALE Width                        | 60     |     | 100  |     | ns    |

| †ALCE             | CE Setup to ALE                  | 5      |     | 30   |     | ns    |

| t <sub>LACE</sub> | CE Hold After ALE                | 40     |     | 45   |     | ns    |

| t <sub>AL</sub>   | Address Setup to ALE             | 20     |     | 50   |     | ns    |

| tLA               | Address Hold After ALE           | 30     |     | 45   |     | ns    |

| tsc               | CS Setup to Read/Write Command   | 20     |     | 50   |     | ns    |

| tcs               | CS Hold After Read/Write Command | 10     |     | 10   |     | ns    |

| tLC               | ALE to Read/Write Command        | 35     |     | 80   |     | ns    |

| t <sub>CL</sub>   | Read/Write Command to ALE        | 0      |     | 0    |     | ns    |

### **WAVEFORMS**

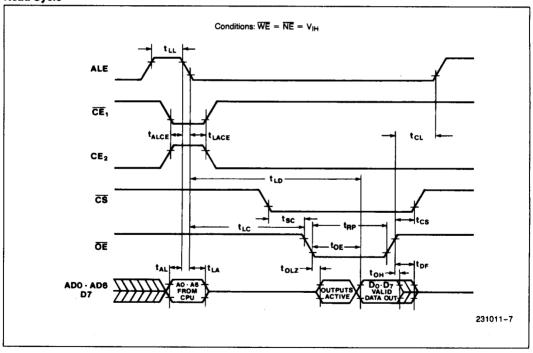

### Read Cycle

### **WAVEFORMS** (Continued)

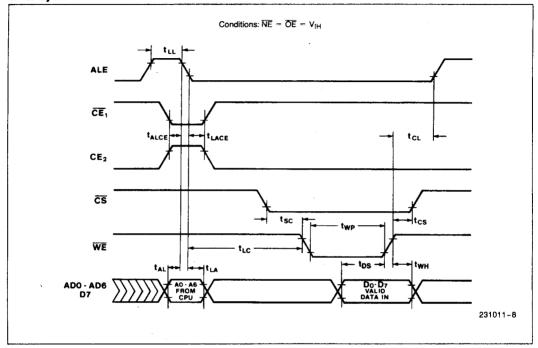

### **Write Cycle**

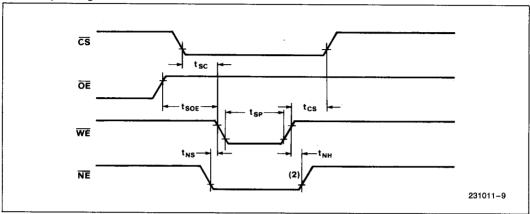

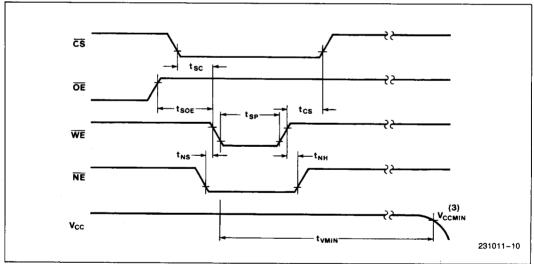

### STORE Operation(1,2)

| Symbol              | Parameter                                                                   | 2001-2 |     | 2001 |     | Units |

|---------------------|-----------------------------------------------------------------------------|--------|-----|------|-----|-------|

| Symbol              | ralameter                                                                   | Min    | Max | Min  | Max | Oints |

| tsc                 | CS Setup Time to STORE Command                                              | 20     |     | 50   |     | ns    |

| tcs                 | CS Hold Time after STORE Command                                            | 10     |     | 10   |     | ns    |

| t <sub>NS</sub>     | NE Setup Time to STORE Command                                              | 0      |     | 0    |     | ns    |

| t <sub>NH</sub>     | NE Hold Time after STORE Command                                            | 0      |     | 0    |     | ns    |

| tsoe                | OE Disable to STORE Initiation Cycle Pulse                                  | 90     |     | 90   |     | ns    |

| t <sub>SP</sub>     | STORE Initiation Cycle Pulse Width                                          | 150    |     | 250  |     | ns    |

| tstR <sup>(3)</sup> | STORE Operation Time                                                        |        | 10  |      | 10  | ms    |

| t <sub>VMIN</sub>   | V <sub>CC</sub> Above V <sub>CCMIN</sub> after STORE Operation is Initiated | 10     |     | 10   |     | ms    |

### NOTES:

During a STORE Initiation Cycle, address/data inputs are ignored.

For a STORE Initiation Cycle, WE must not go low before NE. Otherwise, a RAM write cycle will result.

Istr begins on the falling edge of WE.

### **WAVEFORMS**

**STORE Initiation Cycle** (1) (See Mode Table Note 2 for ALE,  $\overline{CE}_1$ , and  $CE_2$  timing)

### **Normal Operating Conditions**

### **System Power Down**

#### NOTES

1. Once a STORE Operation has begun, all inputs are ignored and the output: are in a high impedance state.

3.  $V_{CCMIN} = 4.75V$  for 5%  $V_{CC}$  specs.

<sup>2.</sup> After either a STORE or a RECALL operation, or after the device has been powered up, a lockout feature on the NE input inhibits subsequent STORE or RECALL initiation cycles until NE is brought back high. The NE input should therefore be brought back high after each STORE or RECALL operation if another STORE or RECALL is to be performed before the system is powered down.

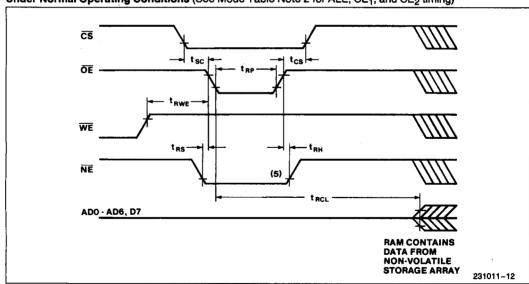

### **RECALL Operation (1)**

| Symbol           | Parameter                                   | 20  | 01-2 | 20  | Units |    |

|------------------|---------------------------------------------|-----|------|-----|-------|----|

| OyDO.            | Talalio Col                                 | Min | Max  | Min | Max   |    |

| tsc              | CS Setup Time to RECALL Command             | 20  |      | 50  |       | ns |

| tcs              | CS Hold Time after RECALL Command           | 10  |      | 10  |       | ns |

| t <sub>RS</sub>  | NE Setup Time to RECALL Command             | 0   |      | 0   |       | ns |

| t <sub>RH</sub>  | NE Hold Time after RECALL Command           | 0   |      | 0   |       | ns |

| tRWE             | WE Disable to RECALL Initiation Cycle Pulse | 90  |      | 90  |       | ns |

| t <sub>RP</sub>  | RECALL Initiation Cycle Pulse Width         | 150 |      | 250 |       | ns |

| t <sub>RCL</sub> | RECALL Operation Time                       |     | 5    |     | 5     | μs |

### Automatic RECALL During System Power Up(2)

### **WAVEFORM**

### Recall Initiation Cycle (4)

### NOTES:

- 1. During a RECALL Initiation Cycle, the address and data inputs are ignored.

- 2. During Automatic Power-Up RECALL, all control signal inputs are ignored.

- 3. V<sub>CCMIN</sub> = 4.75V for 5% V<sub>CC</sub> specification.

- 4. Once a RECALL Operation has begun all inputs are ignored and the outputs are in a high impedance state.

- 5. After either a STORE or a RECALL operation, or after the device has been powered up, a lockout feature on the  $\overline{\text{NE}}$  input inhibits subsequent STORE or RECALL initiation cycles until  $\overline{\text{NE}}$  is brought back high. The  $\overline{\text{NE}}$  input should therefore be brought back high after each STORE or RECALL operation if another STORE or RECALL is to be performed before the system is powered down.

# EXTENDED TEMPERATURE (EXPRESS) EPROMS

The Intel EXPRESS NVRAM family is a series of non-volatile random access memories which have received additional processing to enhance product characteristics. EXPRESS processing is available for several densities of NVRAM, allowing the choice of appropriate memory size to match system applications. EXPRESS NVRAM products are available

with 168 ±8 hour, 125°C dynamic burn-in using Intel's standard bias configuration. This process exceeds or meets most industry specifications of burn-in. The standard EXPRESS NVRAM operating temperature range is 0°C to 70°C. Extended operating temperature range (-40°C to +85°C) EXPRESS products are available. Like all Intel NVRAMs, the EXPRESS NVRAM family is inspected to 0.1% electrical AQL. This may allow the user to reduce or eliminate incoming inspection testing.

### **EXPRESS NVRAM PRODUCT FAMILY**

### **Product Definitions**

| Туре | Operating Temperature | Burn-in 125° (hr) |

|------|-----------------------|-------------------|

| Q    | 0°C to +70°C          | 168 ±8            |

| Т    | -40°C to +85°C        | None              |

| L    | -40°C to +85°C        | 168 ±8            |

### **PACKAGING OPTIONS**

### 2001 Versions

| Packaging Options |               |         |  |  |  |  |

|-------------------|---------------|---------|--|--|--|--|

| Speed Versions    | Cerdip        | Plastic |  |  |  |  |

| -2                | Comm, T, Q, L | Comm    |  |  |  |  |

| -STD              | Comm, T, Q, L | Comm    |  |  |  |  |

Comm = Commercial (0°-70°C) devices