# Am79C900 Integrated Local Area Communications Controller™ (ILACC™)

| Distinctive Characteristics1-5           |            |

|------------------------------------------|------------|

| General Description1-5                   | 1          |

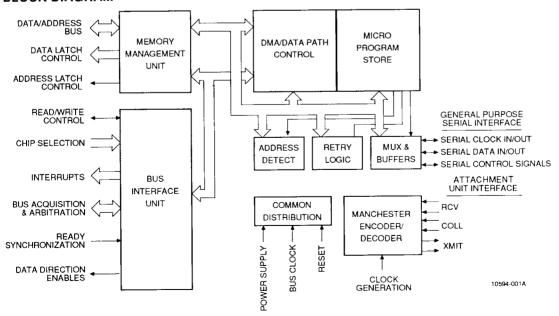

| Block Diagram1-5                         | 1          |

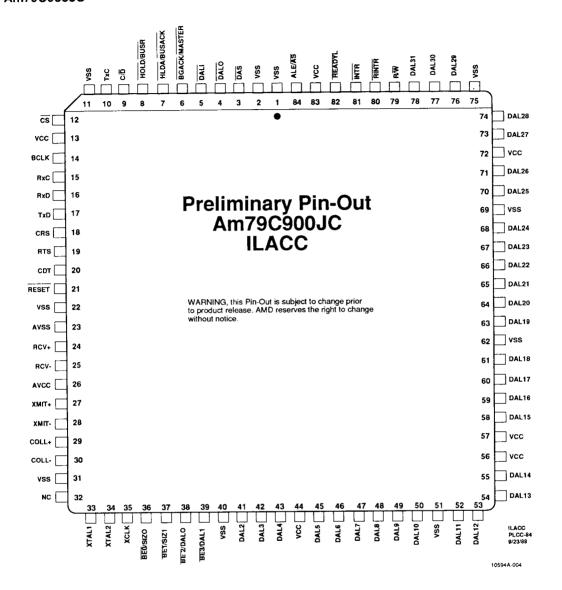

| Connection Diagram1-5                    | 2          |

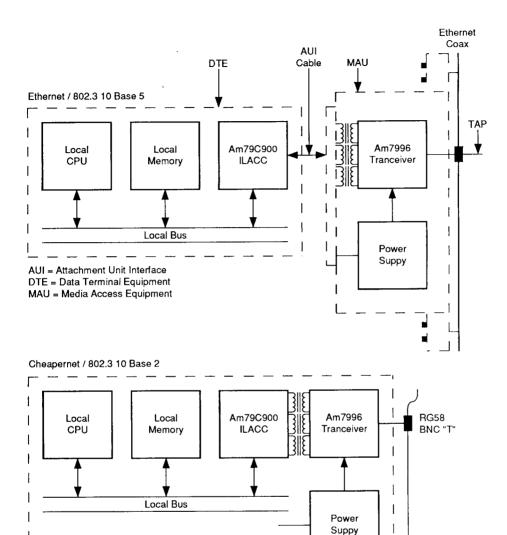

| Typical Ethernet Node1-50                | 3          |

| Ordering Information1-5                  | 4          |

| Pin Description1-55                      | 5          |

| Functional Description1-50               | 8          |

| General1-5                               | 8          |

| ILACC Bus Configurations1-5              | 8          |

| Bus Cycles1-5                            | 9          |

| Bus Slave Cycles1-5                      | 9          |

| Read Sequence1-5                         |            |

| Write Sequence1-5                        | 9          |

| Bus Acquisiton1-5                        | 9          |

| Bus Master Cycles1-5                     | 9          |

| Single Cycle DMA transfers1-5            | 9          |

| Dual DMA Transfers1-6                    | 0          |

| Burst Cycle DMA Transfers1-6             |            |

| Bus Master Transactions1-6               | 0          |

| Initialization Block Access1-6           |            |

| Descriptor Access1-6                     | 0          |

| Data Buffer Access1-6                    |            |

| Detailed Description of Bus Signals1-6   | ;1         |

| Bus Acquisition1-6                       |            |

| Read Sequence1-6                         | ;2         |

| Write Sequence1-6                        | 32         |

| Summary of 32-Bit Memory Transfers1-6    | 32         |

| Initialization Block1-6                  | 32         |

| Transmit/Receive Descriptors1-6          |            |

| Transmit/Receive Buffers1-6              |            |

| FIFO Operations1-6                       |            |

| Transmit1-6                              |            |

| Receive1-6                               |            |

| Serial Interface1-6                      |            |

| General Purpose Serial Interface1-6      | 34         |

| Serial Interface Adapter1-6              | <u>3</u> ∠ |

| SIA-Controller Interface1-6              |            |

| Transmit Path1-6                         |            |

| Transmitter Timing and Operation1-6      |            |

| SIA Oscillator1-6                        |            |

| External Crystal Characteristics1-6      |            |

| External Clock Drive Characteristics 1-6 | 65         |

| Receiver Pain                                           | I-bɔ  |

|---------------------------------------------------------|-------|

| Input Signal Conditioning                               | 1-66  |

| Clock Acquisition                                       | 1-66  |

| PLL Tracking                                            | 1-66  |

| Carrier Tracking and End of Message                     | 1-66  |

| Data Decoding                                           | 1-66  |

| Differential Input Termination                          |       |

| Collision Detection                                     |       |

| Jitter Tolerance Definition                             |       |

| Data Flow Overview                                      |       |

| Descriptor Ring Access Mechanism – Detailed Description |       |

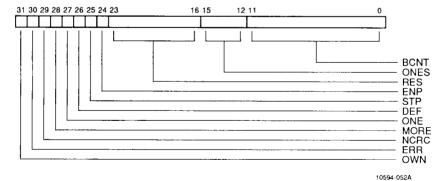

| Transmit Descriptor Table Entry                         |       |

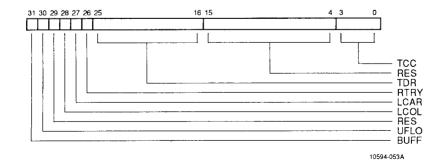

| Receive Descriptor Table Entry                          |       |

| Serial Transmission                                     |       |

| Serial Reception                                        |       |

| Frame Formatting                                        |       |

| Transmit                                                |       |

|                                                         |       |

| Receive                                                 |       |

| Error Reporting and Diagnostics                         |       |

| Error Reporting                                         |       |

| Framing Error (Dribbling Bits)                          |       |

| Loss of Carrier                                         |       |

| Diagnostics                                             |       |

| Loopback                                                |       |

| Interpacket Gap Time (IPG)                              |       |

| General Purpose Serial Interface                        |       |

| Internal SIA Interface                                  |       |

| Collision Detection and Collision Jam                   | 1-71  |

| General Purpose Serial Interface                        | 1-71  |

| Internal SIA Interface                                  | 1-71  |

| Receive-Based Collision                                 | 1-71  |

| Transmit-Based Collision                                | 1-71  |

| Collision-Microcode Interaction                         | 1-71  |

| Time Domain Reflectometry                               | 1-71  |

| Heartbeat                                               |       |

| General Purpose Serial Interface                        |       |

| Internal SIA                                            |       |

| Cyclic Redundancy Check (CRC)                           |       |

| Programmable Resources                                  |       |

| User-Programmable Registers                             |       |

| Control and Status Registers                            |       |

| Jser-Readable Registers                                 |       |

| nitialization                                           |       |

| Reinitialization                                        |       |

| Buffer Management                                       |       |

|                                                         |       |

| Description Memory Allocation                           |       |

| Absolute Maximum Ratings                                |       |

| Operating Ranges                                        |       |

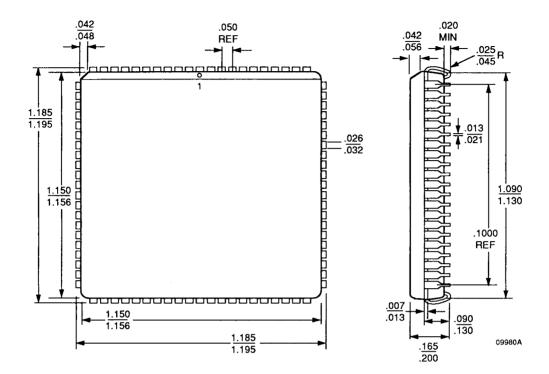

| Physical Dimensions                                     | 1-108 |

# Am79C900

# Advanced Micro Devices

# Integrated Local Area Communications Controller<sup>TM</sup> (ILACC<sup>TM</sup>)

# DISTINCTIVE CHARACTERISTICS

- Integrated Ethernet controller and Serial Interface Adapter.

- 32-bit bus interface with programmable capability for easy interface to popular bus architectures such as: 29000, 80X86, 680X0.

- Compatible with Ethernet and ISD 8802-3 ANSI/ IEEE Std. 802.3 10BASE-5, 10BASE-2, 10BASE-T and 10BASE-F.

- On board 48-byte FIFO, DMA controller, and advanced buffer management scheme.

- Split bus and network clock signals supporting 1-10 Mbit/s networks.

- Extensive network diagnostics capabilities including: CRC, loop back, collision retry/runt packet counters, and TDR.

- State of the art CMOS technology and surface mount packaging.

# **GENERAL DESCRIPTION**

The Am79C900 Integrated Local Area Communications Controller (ILACC) is a second generation Ethernet/802.3 integrated controller and serial interface encoder/decoder. The ILACC has been designed to easily interface to popular microprocessor bus architectures through its programmable bus interface. The ILACC's on board DMA controller and its sophisticated buffer management scheme allows the system designer to achieve maximum performance in tightly coupled systems such as PC mother board applications and node processor based adapter cards. In open bus architec-

tures such as personal computer add-on LAN cards the ILACC gives the system designer the flexibility to chose the optimal cost-performance ratio by allowing both inexpensive bus master and shared memory applications. The ILACC will through its AUI interface in conjunction with an external transceiver chip support thick coax, thin coax, twisted pair and fiber optic cable, networking schemes, such as Ethernet and ISO 8802-3 ANSI/IEEE Std. 802.3 10BASE-5, 10BASE-2, 10BASE-T and 10BASE-F.

## **BLOCK DIAGRAM**

# CONNECTION DIAGRAM Am79C900JC

# TYPICAL ETHERNET NODE

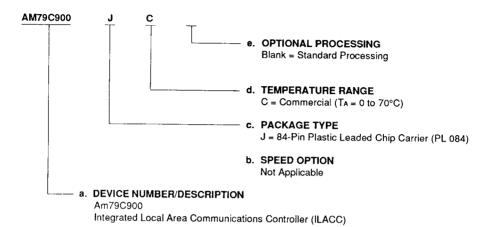

# **ORDERING INFORMATION**

# Standard Products

AMD standard products are available in several Packages and operating ranges. The ordering number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid Con | nbinations |

|-----------|------------|

| AM79C900  | JC         |

# Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

# PIN DESCRIPTION

# ALE.AS

# Address Latch Enable/Address Strobe

(Input/Output, High Impedance)

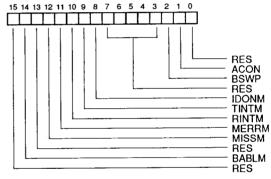

Used to demultiplex the DAL bus and define the address portion of the memory cycle.  $\overline{AS}$  is the logical inversion of ALE. The polarity of the pin is programmable through ACON (CSR3 bit 1) as follows:

ACON = 0: ALE (falling edge latches address). ACON = 1: AS (rising edge latches address).

Used as input during bus arbitration, to detect completion of previous bus master transactions.

# **BCLK**

# **Bus Clock (Input)**

BCLK determines the operating clock rate for the microprocessor interface. The minimum permitted frequency for BCLK must be at least 1.2 times the network data rate, within the range of 2 to 20 MHz. When using the internal SIA, this correlates to 0.6 times the frequency provided at XTAL1/2 (i.e., for a network data rate of 10 Mbits/s, XCLK = 20 MHz, BCLK (min) = 12 MHz, BCLK (max) = 20 MHz).

# **BGACK, MASTER**

# Bus Grant Acknowledge (Input/Output, Open Drain)

Bus Grant Acknowledge indicates the current bus master (BACON = 01). If the ILACC has requested the bus (asserted BUSREQ), it must wait until BUSACK becomes asserted (indicating the current master will relinquish the bus on completion of its transaction), at which time the ILACC will sample BGACK, DAS and ALE/AS. If they are in their inactive state (indicating the current master has completed its last cycle and no other device is claiming bus mastership), the ILACC will assert BGACK. Bus Grant Acknowledge must remain asserted as long as the ILACC remains bus master. Used with 680X0 family of processors.

## Master (Output, Open Drain)

Asserted when ILACC is the bus master (BACON=00) to enable data/address bus drivers.

#### C/D

## Control/Data Select (Input)

Used during slave cycles to determine if the current I/O transaction is transferring control or data information.

$C/\overline{D} = 0$ : Data Port select.

$C/\overline{D} = 1$ : Register Address Port select.

The input is ignored when the ILACC is a bus master.

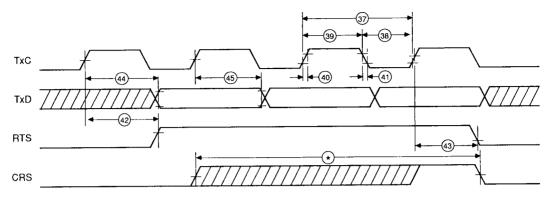

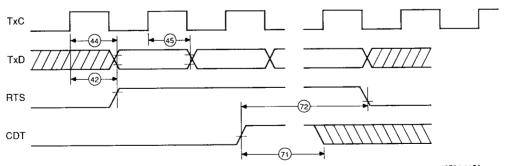

#### CDT

## **Collision Detect (Input)**

When asserted, indicates that there is more than one node transmitting on the medium concurrently. CDT is only required when using the general purpose serial interface. CDT should be tied low when using the internal SIA (PORTSEL = 0, CSR15 bit 8).

# COLL+

# Collision Detect (Input)

A differential line input signaling that there is a collision, when operating the integrated SIA. Used in Ethernet/802.3 applications. Operates at pseudo-ECL levels. When using the general purpose serial interface (PORTSEL = 1, CSR15 bit 8), COLL+/- should be tied to ground

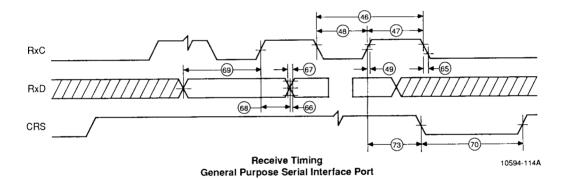

#### **CRS**

# Carrier Sense (Input)

CRS must be asserted when valid data is being received by an external transceiver connected via the general purpose interface port. CRS is only required when using the general purpose serial interface. CRS should be tied low when using the internal SIA (PORTSEL = 0, CSR15 bit 8).

# CS

# ChipSelect(Input)

Used to access the ILACC internal registers, in conjunction with  $C/\overline{D}$ . Ignored during bus mastership cycles.

# DAL -DAL, BE - BE,

# Data/Address/Byte enable lines (Input/Output, High Impedance)

For BACON = 00. In master cycles, during the address portion of a memory transfer, the pins function as  $\overline{BE}_2 - \overline{BE}_3$ , the memory bank selected signals for an 80X86-type environment. During the data portion of the memory transfer,  $DAL_0 - DAL_1$  contain the read or write data, depending on the type of transfer. In slave cycles, these lines operate as data/address lines.

**Data/Address lines (Input/Output, High Impedance)** For BACON = 01. In master cycles, during the address portion of a memory transfer, the pins function as  $A_1$  and  $A_0$ , the byte offset signals for a 680X0-type environment. During the data portion of the memory transfer, DAL $_{0-1}$  contain the read or write data, depending on the type of transfer. In slave cycles, these lines operate as data/address lines.

# DAL,-DAL31

Data/Address Lines (Input Output, High Impedance) During the address portion of a memory transfer DAL<sub>2</sub>–DAL<sub>31</sub> contain memory address information. During the data portion of the memory transfer DAL<sub>2</sub>–DAL<sub>31</sub> contain the read or the write data depending on the type of transfer.

# DALI

# Data/Address Line In (Output)

An external bus transceiver control line, used to enable the data path into the ILACC. Active in both master and slave cycles.

# PIN DESCRIPTION

# ALE.AS

# Address Latch Enable/Address Strobe (Input/Output, High Impedance)

Used to demultiplex the DAL bus and define the address portion of the memory cycle.  $\overline{AS}$  is the logical inversion of ALE. The polarity of the pin is programmable through ACON (CSR3 bit 1) as follows:

ACON = 0: ALE (falling edge latches address).

ACON = 1: AS (rising edge latches address).

Used as input during bus arbitration, to detect completion of previous bus master transactions.

#### **BCLK**

#### **Bus Clock (Input)**

BCLK determines the operating clock rate for the microprocessor interface. The minimum permitted frequency for BCLK must be at least 1.2 times the network data rate, within the range of 2 to 20 MHz. When using the internal SIA, this correlates to 0.6 times the frequency provided at XTAL1/2 (i.e., for a network data rate of 10 Mbits/s, XCLK = 20 MHz, BCLK (min) = 12 MHz, BCLK (max) = 20 MHz).

# **BGACK, MASTER**

# Bus Grant Acknowledge (Input/Output, Open Drain)

Bus Grant Acknowledge indicates the current bus master (BACON = 01). If the ILACC has requested the bus (asserted BUSREQ), it must wait until BUSACK becomes asserted (indicating the current master will relinquish the bus on completion of its transaction), at which time the ILACC will sample BGACK, DAS and ALE/AS. If they are in their inactive state (indicating the current master has completed its last cycle and no other device is claiming bus mastership), the ILACC will assert BGACK. Bus Grant Acknowledge must remain asserted as long as the ILACC remains bus master. Used with 680X0 family of processors.

#### Master (Output, Open Drain)

Asserted when ILACC is the bus master (BACON=00) to enable data/address bus drivers.

#### $C/\overline{D}$

#### Control/Data Select (Input)

Used during slave cycles to determine if the current I/O transaction is transferring control or data information.

$C/\overline{D} = 0$ : Data Port select.

$C/\overline{D} = 1$ : Register Address Port select.

The input is ignored when the ILACC is a bus master.

# CDT

# **Collision Detect (Input)**

When asserted, indicates that there is more than one node transmitting on the medium concurrently. CDT is only required when using the general purpose serial interface. CDT should be tied low when using the internal SIA (PORTSEL = 0, CSR15 bit 8).

# COLL+

# **Collision Detect (Input)**

A differential line input signaling that there is a collision, when operating the integrated SIA. Used in Ethernet/802.3 applications. Operates at pseudo-ECL levels. When using the general purpose serial interface (PORTSEL = 1, CSR15 bit 8), COLL+/- should be tied to ground.

#### **CRS**

# Carrier Sense (Input)

CRS must be asserted when valid data is being received by an external transceiver connected via the general purpose interface port. CRS is only required when using the general purpose serial interface. CRS should be tied low when using the internal SIA (PORTSEL = 0, CSR15 bit 8).

# CS

# ChipSelect(Input)

Used to access the ILACC internal registers, in conjunction with  $C/\overline{D}$ . Ignored during bus mastership cycles.

# DAL -DAL, BE -BE,

# Data/Address/Byte enable lines (Input/Output, High Impedance)

For BACON = 00. In master cycles, during the address portion of a memory transfer, the pins function as  $\overline{BE_2} - \overline{BE_3}$ , the memory bank selected signals for an 80X86-type environment. During the data portion of the memory transfer,  $DAL_0$ - $DAL_1$  contain the read or write data, depending on the type of transfer. In slave cycles, these lines operate as data/address lines.

# **Data/Address lines (Input/Output, High Impedance)** For BACON = 01. In master cycles, during the address portion of a memory transfer, the pins function as $A_1$ and $A_0$ , the byte offset signals for a 680X0-type environment. During the data portion of the memory transfer, DAL $_{0-1}$ contain the read or write data, depending on the type of transfer. In slave cycles, these lines operate as data/address lines.

# DAL,-DAL,

Data/Address Lines (Input Output, High Impedance)

During the address portion of a memory transfer

DAL<sub>2</sub>-DAL<sub>31</sub> contain memory address information. During the data portion of the memory transfer DAL<sub>2</sub>-DAL<sub>31</sub>

contain the read or the write data depending on the type of transfer.

#### DΔL

# Data/Address Line In (Output)

An external bus transceiver control line, used to enable the data path into the ILACC. Active in both master and slave cycles.

1-55

## DALO

## Data/Address Line Out (Output)

An external bus transceiver control line, used to enable the data path away from the ILACC. Active in both master and slave cycles.

# DAS

# Data Strobe (Input/Output, High Impedance)

Defines the data portion of the bus transfer. Input during bus slave, output during bus master cycles.

#### HLDA.BUSACK

#### Hold Acknowledge (Input)

Response from other potential bus masters to indicate they have relinquished bus mastership, in an 80X86-type processor environment (BACON = 00). Any host which allows preemptive DMA may deassert Hold Acknowledge at any time, requiring the ILACC to deassert  $\overline{\text{HOLD}}$ .

#### Bus Acknowledge (Input)

This signal is asserted by the host in response to a Bus Request. When Bus Acknowledge is received in response to the chip's assertion of Bus Request, the ILACC becomes the bus master after ALE/AS, DAS and BGACK are sampled inactive. Intended for use in 680X0-type processor environments (BACON = 01).

# HOLD.BUSREQ

# Hold (Output, Open Drain)

Asserted by the ILACC to request bus mastership in 80X86 processor configurations. The output can be wire-ORed with other potential bus masters. HOLD will be deasserted by the ILACC within a maximum of five bus cycles, if another master preempts the ILACC (removes HLDA).

# **Bus Request (Output Open Drain)**

Bus Request is asserted when the chip requires the bus for direct memory transfer in 680X0-type processor configurations. The output may be wire-ORed with other potential bus masters.

# INTR

#### Interrupt (Output, Open Drain)

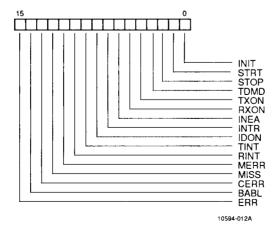

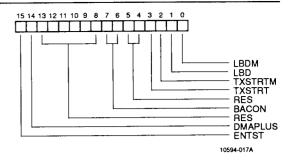

An attention signal that indicates that one or more of the following status flags are set: BABL, MERR, MISS, TINT, IDON (all in CSR0), TXSTRT or LBD (in CSR4). INTR is enabled by IENA = 1 (CSR0 bit 6).

#### NC

#### No Connection

Do not connect.

# **RCV**±

#### Receive Data (Input)

A differential line input to the integrated SIA, for receiving Manchester encoded data from the network. Operates at pseudo-ECL levels. When using the general purpose serial interface (PORTSEL = 1, CSR15 bit 8), RCV  $\pm$  should be tied to ground.

#### R/W

#### Read/Write (Input/Output, High Impedance)

Indicates the direction of data flow to or from the ILACC. An output during bus master cycles, an input during slave cycles.

#### READYL

## Ready Low (Input/Output Open Drain)

When the ILACC is a bus slave, READYL is the output used to request wait states to be inserted in host read/write operations. When the ILACC is a bus master, READYL is the input acknowledge from target memory to indicate it will accept data in a write cycle, or that valid data is available on the DAL bus in a read cycle.

#### RESET

# System Reset (Input)

Reset clears the internal logic. All outputs go to their high impedance state or are driven inactive. All bus-related outputs are high impedance until the Initialize command is given by the host.

#### RINTR

# Receive Interrupt (Output, Open Drain)

When active, indicates that RINT in CSR0 is set (bit 10). RINTR is enabled by INEA (CSR0 bit 6). Receive interrupts can be masked by setting the mask bit RINTM in CSR3 (bit 7). RINTR will remain asserted until RINT is cleared, RINTM is set, or INEA is cleared. RINT set in CSR0 does not cause the external INTR to become asserted, although the INTR summary bit in CSR0 will be set, providing RINTM in CSR3 is clear.

#### RTS

#### Request To Send (Output)

RTS is asserted when the chip wishes access to the channel. RTS remains asserted during the transmission cycle. RTS will only be activated by the ILACC if the general purpose serial interface has been selected. RTS should be left unconnected if the integral SIA has been selected (PORTSEL = 0, CSR15 bit 8).

# RxC

#### Receive Clock (Input)

The receive data clock; operates at the network data rate. Only required if the general purpose serial interface has been selected. Input frequency range from 1 to 10 MHz is permitted. RxC should be tied low if the internal SIA has been selected (PORTSEL = 0, CSR15 bit 8).

#### RxD

#### Receive Data (Input)

The receive serial data path to the general purpose serial interface. Serial data presented on this input will be clocked into the ILACC by the positive edge of the RxC. RxC should be tied low when using the internal SIA (PORTSEL=0, CSR15 bit 8).

# SIZ,-SIZ, BE,-BE,

Size (Output, High Impedance)

With BACON = 01,  $SIZ_0$  and  $SIZ_1$  are produced for 680X0 or Am29000 environments.

# Byte Enable (Output, High Impedance)

With BACON = 00 , these lines become  $\overline{BE}_0$  and  $\overline{BE}_1$  (DAL<sub>0</sub> and DAL<sub>1</sub> become BYTE ENABLE 2 and 3 respectively). These signals are used for the 80X86 interface.

#### TxC

## Transmit Clock (Input)

The transmit data clock, operates at the network data rate. Only required if the general purpose serial interface has been selected. Input frequency range from 1 to 10 MHz is permitted. TxC should be tied low if the internal SIA has been selected (PORTSEL = 0, CSR15 bit 8).

#### TxD

# Transmit Data (Output)

The transmit serial data path. Only activated by the ILACC if the general purpose serial interface has been selected. The ILACC will clock out serial data onto TxD on the positive edge of TxC. TxD should be left unconnected if the internal SIA has been selected (PORTSEL = 0, CSR15 bit 8).

#### VCC

## Power supply (6 pins)

+5 V supply for internal interface logic and I/O pin driver functions.

#### **VSS**

# Ground (10 pins).

0 V reference for internal interface logic and I/O pin driver functions.

## **AVCC**

# **Analog Power supply**

$_{+}5$  V supply for the analog functions of the internal SIA. This supply should be separated from the digital  $\rm V_{cc}$  supplies as far back to the system power supply as practical.

# **AVSS**

# **Analog Ground Reference**

0 V reference for the analog functions of the internal SIA. This ground reference should be separated from the digital  $V_{ss}$  supplies as far back to the system power supply as practical.

#### **XCLK**

# Clock (Output)

XCLK is derived from the crystal oscillator. It can be used as the input to BCLK. Frequency range for XCLK is 2 to 20 MHz.

#### XMIT+

#### XMIT-

# Transmit Data (Output)

A differential line output for transmitting Manchester encoded data from the integrated SIA. Operates at pseudo-ECL levels. When using the general purpose serial interface port (PORTSEL = 1, CSR15 bit 8), XMIT+ should be left unconnected.

# XTAL1

# Crystal Oscillator (Input)

The crystal frequency determines the network data rate. When using an external crystal, two 100-pF capacitors are required, between XTAL1 and ground and XTAL2 and ground. XTAL1 may be driven from an external source, in which case XTAL2 must be left floating. Frequency range is 2 to 20 MHz. When using the internal SIA, the network data rate will be one half of the external crystal frequency. The frequency at XTAL1 cannot run faster than 1.67 times the frequency at BCLK.

# **FUNCTIONAL DESCRIPTION**

# General

The Am79C900 (ILACC) is designed to operate in an environment that allows close coupling with a local memory and/or microprocessor (host), or alternately it can reside on a system bus and act as an intelligent bus master device.

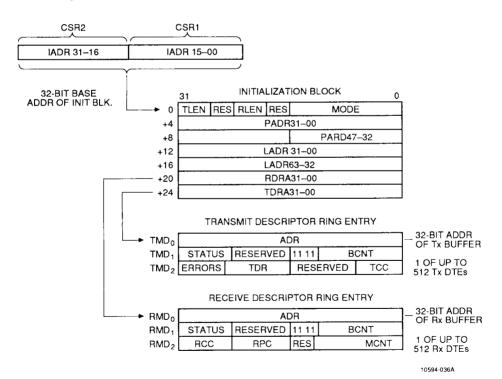

The ILACC is programmed by a combination of registers resident within the chip, and data structures located in user memory. There are 59 user-accessible Control and Status Registers (CSRs) within the chip. The host is responsible for initial programming of a small subset. Once enabled, the ILACC accesses memory directly to acquire additional operating parameters.

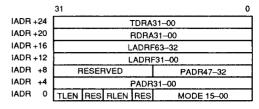

The Am79C900 has the ability to perform independent buffer management as well as transfer data packets to and from the network. There are three memory structures accessed by the chip:

- 1. Initialization Block Seven 32-bit entries in memory starting on a long word boundary. It contains the parameters necessary for device operation. The Initialization Block is comprised of:

- Mode of Operation

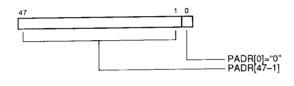

- · Physical Address

- · Logical Address Filter

- Pointers to Receive and Transmit Descriptor Rings

- Number of Entries in Receive and Transmit Descriptor Rings

- Receive and Transmit Descriptor Rings Two

contiguous ring structures in memory, for control of

Receive and Transmit packets. The descriptor rings

are comprised of:

- · The address of a data buffer

- Status and error information associated with the buffer

- The length of the data buffer

- Data buffers Area(s) of memory reserved for packet buffering. Data buffers may begin on arbitrary word boundaries. Each buffer must be contiguous in memory, although multiple buffers can be located anywhere in addressable memory.

In general the programming sequence of the ILACC may be summarized as:

- Program the ILACC's CSRs to locate the Initialization Block in memory. The byte control, byte addressing, address latch enable and bus arbitration modes are also defined.

- 2. Define the byte control, byte addressing, address latch, and bus arbitration.

- 3. Fetch the Initialization Block via DMA.

- Access the descriptor rings and data buffers for packet handling.

The parallel interface of the ILACC has been designed to be easily interfaced to a variety of popular 32-bit microprocessor buses; examples include the 80X86, 680X0 and AMD 29000 series. The ILACC is user-configurable so that it directly interfaces to the bus arbitration schemes of the above architectures.

The ILACC has a 32-bit wide linear address space when acting as Bus Master, allowing it to DMA directly into the entire address space of the above microprocessors and system buses.

Interrupts to the processor are generated by the ILACC upon:

- 1. Completion of ILACC's Initialization routine

- 2. The reception of a packet

- 3. Start of transmit packet

- 4. Completion of transmit activity

- 5. A transmitter time-out error

- 6. A missed packet

- 7. A memory error

- 8. Completion of a loopback test

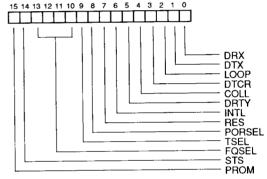

The cause of interrupt is determined by reading CSR0 and/or CSR4. Bit 6 of CSR0 (INEA) enables or disables interrupts to the host. In systems where polling is used in place of interrupts, bit 7 of CSR0 (INTR) indicates an interrupt condition.

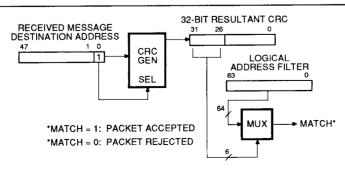

The basic operation of the ILACC consists of two distinct modes: transmit and receive. In the transmit mode, the ILACC directly addresses data in a transmit buffer in memory. It prefaces the data with a preamble and synchronization pattern, and calculates and appends a 32-bit CRC. This packet is then Manchester encoded by the internal SIA, or sent out in NRZ format with clock, depending on which transceiver port is selected.

In the receive mode, packets are received via the external transceiver and passed to either the SIA port or the general purpose serial interface of the ILACC. If the internal SIA is used, clock and data separation occur and the packet is loaded into buffer memory. If the general purpose interface is used, clock and data separation must occur externally. A CRC is calculated for the received packet and compared with the CRC appended to the data packet. If the calculated CRC does not agree with the packet CRC, an error bit is set.

# **ILACC Bus Configurations**

The ILACC supports a 32-bit data and address bus. Memory byte selection during ILACC bus mastership can be software-programmed according to the target microprocessor using the BACON bits. Arbitration schemes for 80X86 and the 680X0 are supported.

# **Bus Cycles**

Depending on the operation, the ILACC can function as a bus slave (memory or I/O mapped) or as a bus master (DMA) device.

#### **BUS SLAVE CYCLES**

Slave cycles are executed by the host system on the ILACC, to program the initial conditions of the device or to examine its state during operation.

The host can gain read or write access to the ILACC's internal Control and Status Registers (CSRs) by asserting the  $\overline{CS}$  line ( $\overline{CS}$  = 0), causing the ILACC to enter the bus slave mode. The CSRs are accessed in a two-stage process. The host must first write the address of the register to be accessed into the Register Address Pointer (RAP). The host can subsequently perform read or write operations on the register addressed by the contents of RAP by accessing the Data Port.

RAP or Data Port selection is performed using the  $C/\overline{D}$  input pin  $(C/\overline{D}=1$  for RAP access). For more details, see the heading "User Programmable Registers."

All slave accesses to/from the ILACC's internal CSRs take place over  $DAL_{0-15}$ . The high order address and data bus lines ( $DAL_{16-31}$ ) are undefined during slave operation.

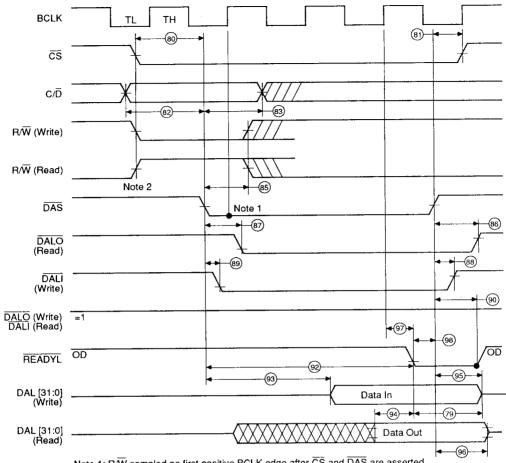

# Read Sequence

At the beginning of the read cycle,  $\overline{CS}$ ,  $\overline{C/D}$  and  $\overline{R/W}$  are asserted by the host. The host will assert  $\overline{DAS}$ , which will latch both the read request and the state of  $\overline{C/D}$  within the ILACC.  $\overline{R/W}$  and  $\overline{C/D}$  need not be active for the remainder of the cycle. The ILACC will subsequently assert  $\overline{DALO}$  to enable the external output bus transceiver(s). If  $\overline{C/D}$  was latched as a "1", the contents of RAP will be placed on the DAL bus. If  $\overline{C/D}$  was a "0", the contents of the CSR addressed by RAP will be placed on the DAL bus. After the data on  $\overline{DALO}$ , and relinquish  $\overline{CS}$ . The ILACC subsequently releases  $\overline{DALO}$ ,  $\overline{READYL}$  and the DAL bus.  $\overline{CS}$  and  $\overline{DAS}$  must be valid during the entire slave read cycle.

# Write Sequence

At the beginning of the write cycle,  $\overline{CS}$ ,  $C/\overline{D}$  and  $R/\overline{W}$  are asserted by the host. The host will assert  $\overline{DAS}$ , which will latch both the write request and the state of  $C/\overline{D}$  within the ILACC.  $R/\overline{W}$  and  $C/\overline{D}$  need not be active for the remainder of the cycle. The ILACC will subsequently assert  $\overline{DALI}$  to enable the external input bus transceiver(s). The host will output the write data on  $DAL_{0.31}$ . If  $C/\overline{D}$  was latched as a "1", the contents of the DAL bus will be written to RAP. If  $C/\overline{D}$  was a "0", the contents of the DAL bus will be written to the CSR addressed by the RAP. When the ILACC asserts  $\overline{READYL}$ , the host strobes the data into the ILACC using the rising edge of  $\overline{DAS}$ , and subsequently

releases the  $\overline{CS}$  line and the DAL bus. The ILACC will deassert  $\overline{DALI}$  and  $\overline{READYL}$  in response to  $\overline{DAS}$  going inactive.  $\overline{CS}$  and  $\overline{DAS}$  must be valid during the entire slave write cycle.

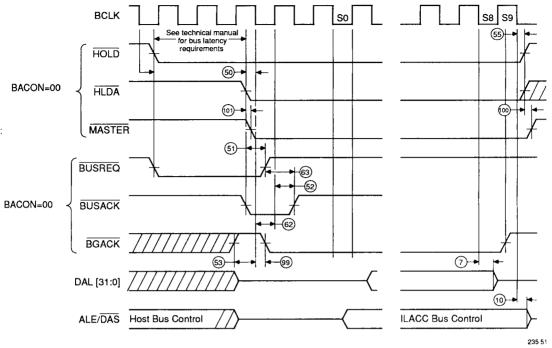

#### **BUS ACQUISITION**

The ILACC bus acquisition mechanism can be optimized to suit common two- or three-wire bus arbitration schemes, using the Bus Acquisition Control (BACON) bits in CSR4, as defined below:

| BACON | Bus Configuration |

|-------|-------------------|

| 00    | 80X86             |

| 01    | 680X0             |

| 10    | RESERVED          |

| 11    | RESERVED          |

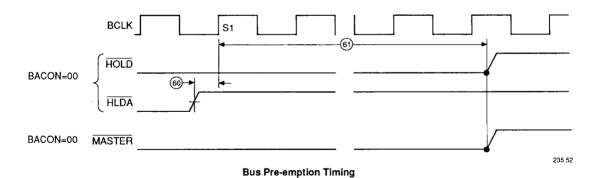

For 80X86-type processors, bus acquisition is controlled with a two-wire handshake of  $\overline{\text{HOLD}}$  (HOLD REQUEST) and  $\overline{\text{HLDA}}$  (HOLD ACKNOWLEDGE). If BACON = 00 (80X86 operation), the burst transfer may be preempted by the host or system arbiter deasserting the  $\overline{\text{HLDA}}$  line. The ILACC will complete its current bus transaction before relinquishing the  $\overline{\text{HOLD}}$  request.

For 680X0-type processors, bus acquisition is controlled with a three-wire handshake of BUSREQ (BUS REQUEST), BUSACK (BUS ACKNOWLEDGE) and BGACK (BUS GRANT ACKNOWLEDGE). Preemption is not supported in this configuration.

The ILACC will request the bus to enable the movement of a receive packet into the receive buffer area, or to check for the presence of a transmit message and to move it from the transmit buffer area if required.

If there are 16 bytes or more empty in the FIFO in transmit mode, or at least 16 bytes of data in the FIFO in receive mode, when the ILACC releases the bus (HOLD or BGACK deasserted), it will request the bus again within 4 bus clock periods for receive, or 10 bus clock periods for transmit.

# BUS MASTER CYCLES (ILACC DMA TRANSFERS)

The ILACC will initiate DMA transfers according to the type of operation being performed. All DMA transfers will fall into the following catagories:

- Single-cycle DMA

- Dua-cycle DMA

- · Burst-cycle DMA

# Single-Cycle DMA Transfers

Once the ILACC has been granted bus mastership, it will issue a single long-word memory address, and perform the read or write operation on the location, with appropriate output signals to indicate selection of the active data bytes during the transfer. On completion of the transfer, the ILACC will relinquish bus mastership.

# **Dual-Cycle DMA Transfers**

Once the ILACC has been granted bus mastership, it will perform two data transfer cycles before relinquishing the bus. It will issue the long-word memory address of the first location, and perform the read/write operation, supplying appropriate output signals to indicate selection of the active data bytes before executing the second transfer in a similar manner and relinquishing the bus. The two transfers within the mastership period will always be of the same type (either both read or both write), but may or may not be to contiguous addresses. Dual-cycle DMA transfers cannot be preempted.

# **Burst-Cycle DMA Transfers**

Once the ILACC has been granted bus mastership, it will perform a series of consecutive data transfer cycles before relinquishing the bus. Each data transfer will be performed sequentially, with the issue of the long-word address, and the transfer of the data with appropriate output signals to indicate selection of the active data bytes during the transfer. All transfers within the mastership cycle will be either read or write cycles, and will be to contiguous long-word addresses. The number of data transfer cycles within the burst is dependent on the programming of the DMAPLUS option (CSR4, bit 14). If DMAPLUS = 0, a maximum of four transfers will be performed. If DMAPLUS = 1, the burst will continue until the FIFO is filled to its high threshold (transmit operation) or emptied to its low threshold (receive operation). The exact number of transfer cycles in this case will be dependent on the latency of the system bus to the ILACC's mastership request (HOLD/BUSREQ to HLDA/ BGACK delay) and the speed of bus operation. The burst cycle may be preempted when using the 80X86 mode of operation by removing the mastership privilege (HLDA = HIGH). The ILACC will complete the current read or write cycle before returning the mastership request inactive (HOLD = HIGH).

# **BUS MASTER TRANSACTIONS**

Transactions during ILACC bus mastership consist of use of the allowable DMA cycle types as previously defined and the type of memory transaction being performed. Bus transactions fall into one of the following three catagories:

- · Initialization block read access

- · Descriptor read/write access

- Data buffer read/write access

# Initialization Block Access

This transaction reads all 7 long-words (28 bytes) of the Initialization Block.

Data is read from the Initialization Block as a sequence of four separate arbitration/relinquish cycles. The first three exchanges will be performed as dual-cycle DMA transfers, performing two contiguous long-word reads, commencing at the base address programmed in CSR1 and CSR2. This sequence continues until the fourth

cycle, which will perform a single-cycle DMA transfer, to read the last long-word entry in the Initialization Block. The time between each mastership cycle may vary if another device is also contending for bus mastership during the initialization sequence. The ILACC will always complete the 2 long-word read operations within the bus mastership period, even if preempted.

Initialization Block entries are not byte-swapped, regardless of target configuration. The internal ILACC registers read in the memory-based initialization parameters on the basis that bit 31 of the memory location is the high order bit of the word.

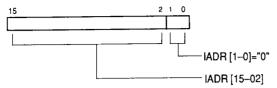

The base location of the Initialization Block is constrained to be on an even word boundary. Bits 0 and 1 of CSR1 must be zero.

# **Descriptor Access**

These transactions read and write the appropriate entries of the transmit and receive descriptor rings to manage the transfer of transmit buffers to the network and messages from the network to the receive buffers.

Accesses to descriptor entries are performed by only two methods:

A single-cycle DMA transfer is used to examine the OWN bit or modify the status in the transmit or receive descriptor (TMD1[31-24], RMD1[31-24]). If ownership is established, a separate single-cycle DMA transfer will be used to read the address of the buffer (TMD2 or RMD2).

For chained buffers (multiple descriptors/buffers containing a single message), a single-cycle write will be used to update the transmit or receive descriptor status (TMD1 or RMD1) of all but the last descriptor in the chain.

A dual-cycle DMA transfer will be performed on a transmit descriptor, if a condition is detected which requires both status (TMD1) and error (TMD2) conditions to be reported. Transmit descriptors will only be updated with a dual-cycle DMA transfer if an error condition is reported and the descriptor is the last or only entry in the transmit chain.

A dual-cycle DMA write will be used on receive descriptors on completion of the receive packet to update the status (RMD1) and report the message length (RMD2) and/or error conditions. Receive descriptors will only be updated with a dual-cycle DMA transfer, if the descriptor is the last or only entry in the receive chain.

Note that during all descriptor read operations, the entire data bus will be activated, as if a full long-word data fetch were being performed. The ILACC will internally route and use only the required data, and discard any superfluous information fields. For write cycles, only the appropriate data bus bytes are activated, to ensure adjacent memory locations are not corrupted.

Descriptor entries are not byte swapped, regardless of target configuration. The internal ILACC registers read in the memory-based initialization parameters on the basis that bit 31 of the memory location is the high order bit of the word.

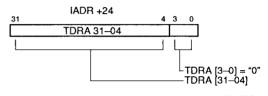

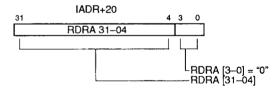

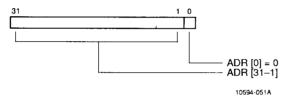

Descriptors must be constrained to be on 16-byte boundary, as defined by the TRANSMIT/RECEIVE DESCRIPTOR RING ADDRESS fields (TDRA and RDRA), within the Initialization Block (TDRA[3-0] = 0, RDRA[3-0] = 0). Hence all descriptor entries will appear on long-word boundaries to the ILACC.

# Data Buffer Access

Burst-cycle DMA is used to read transmit buffer information and transfer it to the FIFO, or to write receive message information from the FIFO to the receive buffer area.

Accesses to buffer entries are performed by only two burst mechanisms:

- If DMAPLUS = 0 (CSR4, bit 14), the burst transfer will consist of up to four read/write cycles, providing the ILACC is not preempted (applicable to 80X86 mode only). If the ILACC is preempted, it will complete its current read/write transfer, before relinquishing mastership.

- If DMAPLUS = 1, burst transfers continue until the FIFO is filled to its high threshold, or emptied to its low threshold, within a single DMA burst cycle (unless preempted). If the ILACC is preempted, it will complete its current read/write transfer, before relinquishing mastership.

To maximize system bus bandwidth, the ILACC will always use its first DMA transfer to or from a buffer, to long-word align its remaining transfers. For example, if the buffer is located on an odd-word boundary (A1 = 1, A0 = 0), the first DMA transfer will read or write 1 word (2 bytes) of data. Subsequent cycles will DMA long-word data (4 bytes) since the addresses will now be longword aligned (A1 = 0, A0 = 0); until the burst is complete, or less than 4 data bytes remain to be DMAed.

In the case where less than 4 bytes remain to be transferred to/from a buffer, the ILACC will read data from or write data to the appropriate bytes of the data bus, in accordance with the relevant host processor addressing convention.

Note that during all buffer read operations, the entire data bus will be activated, as if a full long-word data fetch were being performed. The ILACC will internally route and use only the required data, and discard any superfluous information fields. For write cycles, only the appropriate data bus bytes are activated, to ensure adjacent memory locations are not corrupted.

Buffer data will be byte swapped according to the target memory architecture, due to the byte orientation of the

802.3 protocol ("little-endien"). Data is transferred across the network in byte-ascending order (i.e., starting with byte 0, then byte 1, 2, 3, etc.).

There are a number of additional restrictions which apply to transmit and receive buffers:

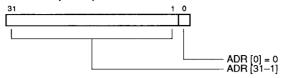

- Buffers must commence on word boundaries (A0 = 0), as defined by the transmit/receive message buffer pointer (ADR[0] = 0 in TMD0 or RMD0).

- 2. The BUFFER BYTE COUNT for receive buffers should always be an even number of bytes (BCNT in RMD1), and must be a minimum of 64 bytes.

- 3. The MESSAGE BYTE COUNT for receive buffers (MCNT in RMD2) will contain the exact number of bytes received in the packet, and is written by the ILACC in the last receive descriptor table entry (DTE) for the message (valid where the ENP bit is set in RMD1, and assuming ERR is clear).

- 4. The BUFFER BYTE COUNT (BCNT in TMD1) for the first buffer in a chained transmit packet must be a minimum of 116 bytes if DMAPLUS (CSR4[14]) is set, or 100 bytes minimum if DMAPLUS is reset. Note that BCNT should be an even number of bytes, except in the case where it refers to the last, or only, buffer in a chain.

Note that 80X86 type processors have bus transfer restrictions, namely:

- (i) that a single 3-byte transfer will not be observed, without an accompanying byte cycle either before or after.

- (ii) misaligned transfers will move the data at the high addressed long-word location first, then decrement to the previous long-word location to complete the transfer.

These restrictions do not apply to the ILACC even when configured for the 80X86 interface. 3-byte cycles can be observed (i.e., at the end of a buffer), and the ILACC will transfer data logically, incrementing to each long word location, and performing the appropriate transfer.

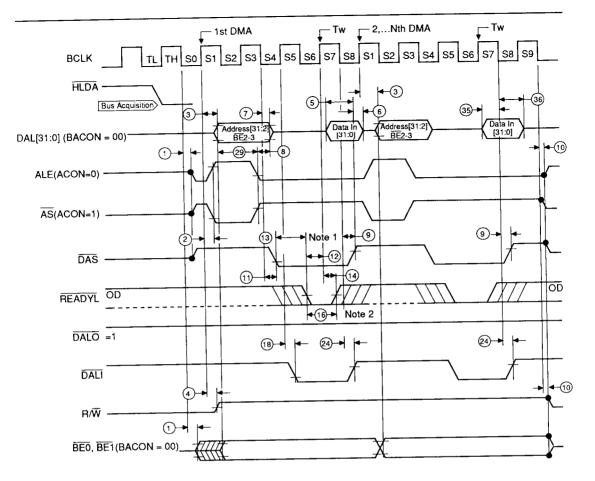

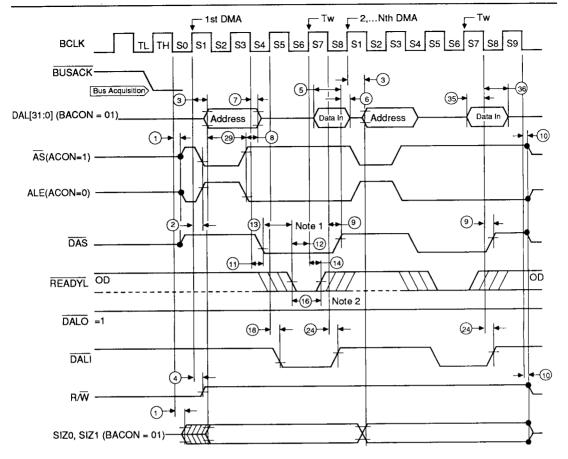

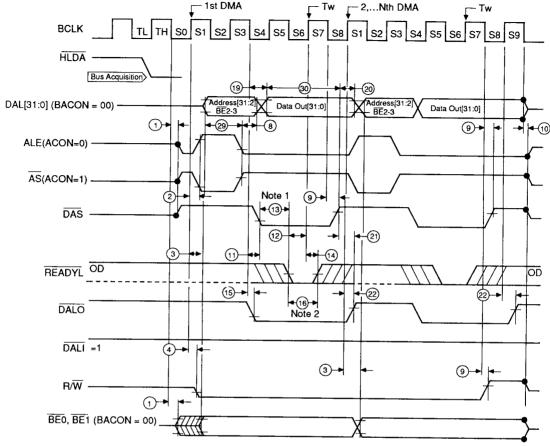

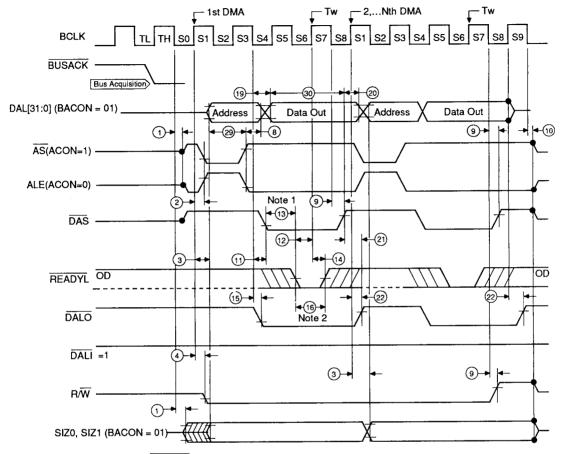

# Detailed Description of Bus Signals Bus Acquisition

All data transfers from the ILACC during bus mastership are timed by ALE/AS or  $\overline{\rm DAS}$ , and  $\overline{\rm READYL}$ . The automatic adjustment of the ILACC cycle by the  $\overline{\rm READYL}$  signal allows synchronization with variable cycle time memory. Bus cycles are a minimum of 4.T<sub>BCLK</sub> cycles and can be increased in 1.T<sub>BCLK</sub> increments.

DALI and DALO are used to control external bus transceivers. DALI is used to enable the data path toward the ILACC, DALO to enable the data path away from the ILACC.

## **Read Sequence**

The read cycle is commenced by placing valid addresses on DAL $_{0.31}$  for the 680X0 mode, or DAL $_{2.31}$  for the 80X86 mode. The appropriate byte transfer signals (A $_{0.1}$  and SIZ $_{0.1}$  for the 680X0 mode;  $\overline{\rm BE}_{0.3}$  for the 80X86 mode) are asserted to indicate the active data bus width. The R/W signal is driven HIGH to indicate a read cycle. The ALE/AS pulse allows the external latch to load and store the long-word address. The DAL lines go into a high impedance state and  $\overline{\rm DAS}$  falls low to signal the start of the memory access.  $\overline{\rm DALI}$  is activated by the ILACC to enable the external input bus transceiver(s). The memory responds by asserting the  $\overline{\rm READYL}$  input to the ILACC, to indicate that  ${\rm DAL}_{0.31}$  have valid data. The ILACC latches the memory data on the rising edge of  $\overline{\rm DAS}$ , which in turn ends the memory cycle.

# Write Sequence

The write cycle is very similar except the write transfer is indicated by R/W being driven LOW. The DAL<sub>0.31</sub> lines change from containing addresses to data after ALE/AS goes inactive. DALO is used to enable the ILACC data onto the data bus. Data to memory is held valid after DAS goes inactive.

# **SUMMARY OF 32-BIT MEMORY TRANSFERS**

From the cases outlined previously, the following set of 32-bit bus transfer conditions are required.

# Initialization Block:

LONG-WORD TRANSFER FROM EVEN-WORD ADDRESS

Example: Normal 32-bit Initialization Block entry read.

680X0: SIZ1=0, SIZ0=0, A1=0, A0=0

| MS       | byte     | from       | DAL <31:24>  |

|----------|----------|------------|--------------|

|          | byte     | from       | DAL <23:16>  |

|          | byte     | from       | DAL <15:08>  |

| LS       | byte     | from       | DAL <07:00>  |

| 80X86: # | BE3=0, # | #BE2=0, #B | E1=0, #BE0=0 |

| MS       | byte     | from       | DAL <31:24>  |

|          | byte     | from       | DAL <23:16>  |

|          | byte     | from       | DAL <15:08>  |

| LS       | byte     | from       | DAL <07:00>  |

|          |          |            |              |

## Transmit/Receive Descriptors:

LONG-WORD TRANSFER TO/FROM EVEN-WORD ADDRESS

Example: Normal 32-bit descriptor access.

680X0: SIZ1=0 SIZ0=0, A1=0, A0=0

| 680X0: S | IZ7=U, S | 51ZU=U, A1=U, AU=U     |

|----------|----------|------------------------|

| MS       | byte     | to/from DAL <31:24>    |

|          | byte     | to/from DAL <23:16>    |

|          | byte     | to/from DAL <15:08>    |

| LS       | byte     | to/from DAL <07:00>    |

| 80X86: # | BE3=0, i | #BE2=0, #BE1=0, #BE0=0 |

| MS       | byte     | to/from DAL <31:24>    |

|          | byte     | to/from DAL <23:16>    |

|          | byte     | to/from DAL <15:08>    |

| LS       | byte     | to/from DAL <07:00>    |

BYTE TRANSFER FROM EVEN-WORD ADDRESS Example: Read status from RMD1/TMD1. 680X0: SIZ1=0, SIZ0=0, A1=0, A0=0

MS byte from DAL <31:24> 80X86: #BE3=0, #BE2=0, #BE1=0, #BE0=0 MS byte from DAL <31:24>

Note: Although all bytes are active, only required bytes are used internally.

BYTE TRANSFER TO EVEN-WORD ADDRESS

Example: Write status to RMD1/TMD1.

680X0: SIZ1=0, SIZ0=1, A1=0, A0=0 MS byte to DAL <31:24>

80X86 : #BE3=0, #BE2=1, #BE1=1, #BE0=1 MS byte to DAL <31:24>

#### Transmit/Receive Buffers :

LONG-WORD TRANSFER TO/FROM EVEN-WORD ADDRESS

Example: First, last or only 4 bytes in buffer on evenword address.

680X0: SIZ1=0, SIZ0=0, A1=0, A0=0

to/from DAL <31:24> FIFO byte n to/from DAL <23:16> **FIFO** byte n + 1 DAL <15:08> **FIFO** byte n + 2 to/from FIFO byte n + 3 to/from DAL <07:00> 80X86: #BE3=0, #BE2=0, #BE1=0, #BE0=0 **FIFO** byte n to/from DAL <07:00> **FIFO** byte n + 1 to/from DAL <15:08>

FIFO byte n to/from DAL <07:00>

FIFO byte n + 1 to/from DAL <15:08>

FIFO byte n + 2 to/from DAL <23:16>

FIFO byte n + 3 to/from DAL <31:24>

3-BYTE TRANSFER FROM EVEN-WORD ADDRESS Example: Last or only 3 bytes in transmit buffer. 680X0; SIZ1=0, SIZ0=0, A1=0, A0=0

FIFO byte n from DAL <31:24>

FIFO byte n + 1 from DAL <23:16>

FIFO byte n + 2 from DAL <15:08>

80X86: #BE3=0, #BE2=0, #BE1=0, #BE0=0 FIFO byte n from DAL <07:00> FIFO byte n + 1 from DAL <15:08>

FIFO byte n + 2 from DAL <23:16>

Note: Although all bytes are active, only required bytes

3-BYTE TRANSFER TO EVEN-WORD ADDRESS Example: Last or only 3 bytes in receive buffer. 680X0: SIZ1=1, SIZ0=1, A1=0, A0=0

are used internally.

FIFO byte n to DAL <31:24> FIFO byte n + 1 to DAL <23:16> DAL <15:08> FIFO byte n + 2 to 80X86: #BE3=1, #BE2=0, #BE1=0, #BE0=0 DAL <07:00> FIFO byte n to **FIFO** byte n + 1 to DAL <15:08> DAL <23:16> FIFO byte n + 2 to

WORD TRANSFER FROM EVEN-WORD ADDRESS Example: Last or only 2 bytes in transmit buffer on

680X0: SIZ1=0, SIZ0=0, A1=0, A0=0

even-word address.

from DAL <31:24> byte n F!FO from DAL <23:16> FIFO byte n + 1 80X86: #BE3=0, #BE2=0, #BE1=0, #BE0=0 from DAL <07:00> FIFO byte n DAL <15:08> from **FIFO** byte n + 1

Note: Although all bytes are active, only required bytes are used internally.

WORD TRANSFER TO EVEN-WORD ADDRESS Example: Last or only 2 bytes in receive buffer on even-word address.

680X0: SIZ1=1, SIZ0=0, A1=0, A0=0

DAL <31:24> **FIFO** byte n to DAL <23:16> to FIFO byte n + 1 80X86: #BE3=1, #BE2=1, #BE1=0, #BE0=0 DAL <07:00> to FIFO byte n DAL <15:08> FIFO to byte n + 1

WORD TRANSFER FROM ODD-WORD ADDRESS Example: First or only 2 bytes in transmit buffer on odd-word address.

680X0: SIZ1=0, SIZ0=0, A1=0, A0=0

DAL <15:08> from FIFO byte n DAL <07:00> **FIFO** byte n + 1 from 80X86: #BE3=0, #BE2=0, #BE1=0, #BE0=0 DAL <23:16> from FIFO byte n DAL <31:24> from FIFO byte n + 1

Note: Although all bytes are active, only required bytes are used internally.

WORD TRANSFER TO ODD-WORD ADDRESS Example: First or only 2 bytes in receive buffer on odd-word address.

680X0: SIZ1=1, SIZ0=0, A1=1, A0=0

DAL <15:08> FIFO byte n to DAL <07:00> byte n + 1 to FIFO 80X86: #BE3=0, #BE2=0, #BE1=1, #BE0=1 DAL <23:16> **FIFO** byte n to DAL <31:24> FIFO byte n + 1 to

BYTE TRANSFER FROM EVEN-WORD ADDRESS Example: Last or only byte in transmit buffer on even-word address.

680X0: SIZ1=0, SIZ0=0, A1=0, A0=0

FIFO byte n from DAL <31:24> 80X86: #BE3=0, #BE2=0, #BE1=0, #BE0=0

FIFO byte n from DAL <07:00> Note: Although all bytes are active, only required bytes are used internally. BYTE TRANSFER TO EVEN-WORD ADDRESS Example: Lastor only byte in receive buffer on even-word address.

680X0: SIZ1=0, SIZ0=1, A1=0, A0=0

FIFO byte n to DAL <31:24> 80X86: #BE3=1, #BE2=1, #BE1=1, #BE0=0

FIFO byte n to DAL <07:00>

BYTE TRANSFER FROM ODD-WORD ADDRESS Example: Last or only byte in transmit buffer on oddword address.

680X0: SIZ1=0, SIZ0=0, A1=0, A0=0

FIFO byte n from DAL <15:08>

80X86: #BE3=0, #BE2=0, #BE1=0, #BE0=0

FIFO byte n from DAL <23:16>

Note: Although all bytes are active, only required bytes are used internally.

BYTE TRANSFER TO ODD-WORD ADDRESS Example: Last or only byte in receive buffer on oddword address.

680X0: SIZ1=0, SIZ0=1, A1=1, A0=0 FIFO byte n to DAL <15:08> 80X86: #BE3=1, #BE2=0, #BE1=1, #BE0=1 FIFO byte n to DAL <23:16>

## FIFO Operations

The FIFO provides temporary buffer storage for data being transferred between the parallel bus I/O pins and serial bus I/O pins. The capacity of the FIFO is 48 bytes.

#### **Transmit**

Data is loaded into the FIFO under internal microprogram control.

The FIFO must be more than 16 bytes empty before the ILACC requests the bus (HOLD/BUSREQ is asserted). The ILACC will start sending the preamble (if the line is idle) as soon as there is one byte loaded into the FIFO. Should the transmitter be required to back off, there will be up to 32 bytes of data in the FIFO ready for transmission. Reception has priority over transmission during the time that the transmitter is backing off.

# Receive

Data is loaded into the FIFO from the serial input shift register during reception and leaves the FIFO under microprogram control. The ILACC microcode will wait until there are at least 16 bytes of data in the FIFO before initiating a DMA burst transfer. Preamble (including the synchronization bits) is not loaded into the FIFO.

# Serial Interface

The ILACC has two serial interfaces:

- · General Purpose Serial Interface

- · IEEE 802.3 Attachment Unit Interface (AUI)

# GENERAL PURPOSE SERIAL INTERFACE

This is provided to allow alternate clock/data encoder transceivers. When the GPSI port is not in use (PORTSEL = 0, CSR15 bit 8), all inputs should be tied low and when all outputs are not in use, it should be left floating.

#### SERIAL INTERFACE ADAPTER

This is a Manchester Encoder/line driver in the transmit path, a Manchester Decoder with noise filtering and quick lock-on characteristics in the receive path, and a signal detect/converter in the collision path. In addition, the integral SIA provides the interface between the CMOS logic environment of the controller and the differential signaling environment of the transceiver.

#### SIA-Controller Interface

Since the ILACC incorporates the facilities of both the LANCE (Am7990) and SIA (Am7992A), the interface signals which previously appeared as hardwired pins are now internal.

To more easily understand the operation of the ILACC, this internal interface is described as a set of signals, defined as follows:

Internal Receive Enable (IRENA) – Analogous to the externally available Carrier Sense (CRS) signal. An output from the SIA to the controller to indicate carrier presence. IRENA goes active when there is a negative transition on RCV+/RCV- that is more negative than the amplitude "Squelch Limit" and meets the pulse width requirements of the input filtering. IRENA goes inactive within 2 bit times of the last positive transition at RCV+/RCV-.

Internal Receive Clock (IRCLK) – The recovered clock from the differential input at RCV+/RCV-. An output from the SIA block to the controller, to clock in the serial bit stream. IRCLK is activated 1/4 bit time after the second negative Manchester preamble clock transition at RCV+/RCV-, and remains active until the end of message.

Internal Receive Data (IRXD) – The recovered serial data stream from the SIA block to the controller section of the ILACC. When IRENA is active, signals at RCV+/RCV- meeting threshold and pulse width requirements will be clocked in by IRCLK and passed to the controller portion of the ILACC.

Internal Transmit Enable (ITENA) – Identical in function to the RTS output. It is asserted (high) by the controller portion to indicate that serial data is available for encoding and driving XMIT+/XMIT-.

Internal Transmit Clock (ITCLK) – An output from the SIA block to the controller, to clock out the serial bit stream and permit output data to be encoded.

Internal Transmit Data (ITXD) – The serial bit stream output from the controller section. When ITENA is active, signals at ITXD will be clocked out by ITCLK and appear as Manchester encoded data at the XMIT+/XMIT- outputs.

Internal Collision Detect (ICLSN) – Identical in function to the externally available CDT input to the ILACC. ICLSN is an output from the SIA block to the controller. When signals at the COLL+/COLL- differential inputs are driven by an external transceiver to indicate a collision, ICLSN will go high.

# Transmit Path

The transmit section encodes separate clock and NRZ data input signals into a standard Manchester serial bit stream. The transmit outputs (XMIT+/XMIT-) are designed to operate into terminated transmission lines. When operating into a 78-ohm terminated transmission line, signaling meets the required output levels and skew for Cheapernet, Ethernet and IEEE-802.3.

# **Transmitter Timing and Operation**

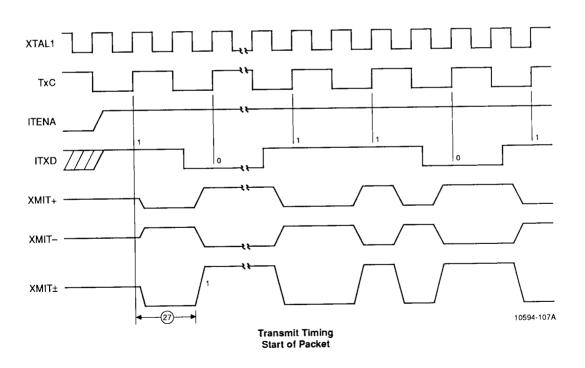

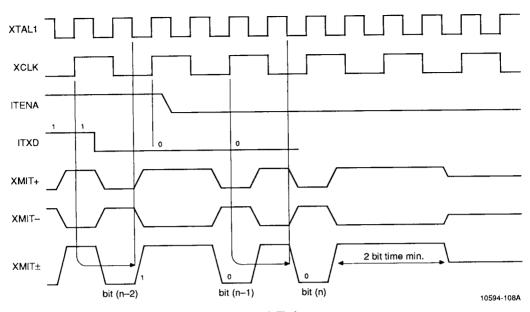

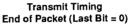

A 20-MHz fundamental mode crystal oscillator provides the basic timing reference (XCLK) for the SIA portion of the ILACC. It is divided by two, to create the internal transmit clock reference (ITCLK). Both XCLK and ITCLK are fed into the SIA's Manchester Encoder to generate the transitions in the encoded data stream. ITCLK is used by the SIA to internally synchronize the Internal Transmit Data (ITXD) from the controller and Internal Transmit Enable (ITENA). ITCLK is also used as a stable bit rate clock by the receive section of the SIA and controller.

The oscillator requires an external 0.005% crystal, or an external TTL-level input as a reference. Transmit accuracy of 0.01% is achieved (no external adjustments are required).

Transmission is enabled by the controller. As long as the ITENA request remains active, the serial output of the controller will be Manchester-encoded and appear at XMIT+ and XMIT-. When the internal request is dropped by the controller, the differential transmit outputs go to one of two idle states, dependent on TSEL in the Mode Register (CSR15, bit 9):

- TSEL LOW: The idle state of XMIT+/XMIT- yields "zero" differential to operate transformer-coupled loads.

- TSEL HIGH: In this idle state, XMIT+ is positive with respect to XMIT- (logical HIGH).

# SIA Oscillator

# **External Crystal Characteristics**

When using a crystal to drive the oscillator, the following crystal specification should be used to ensure a transmit accuracy of 0.01%:

|                                          | Min            | Nom   | Max | Units |

|------------------------------------------|----------------|-------|-----|-------|

| Parallel Resonant Frequency              | 2              |       | 20  | MHz   |

| 2. Resonant Frequency Error (CL = 50 pF) | -50            | 0     | +50 | PPM   |

| 3. Change in Resonant Frequency          | -40            |       | +40 | PPM   |

| With Respect To Temperature (CL = 50 pF  | <del>:</del> ) |       |     |       |

| 4. Motional Crystal Capacitance (C1)     |                | 0.022 |     | рF    |

| 5. Series Resistance                     |                |       | 35  | Ω     |

| 6. Shunt Capacitance                     |                |       | 7   | pF    |

| 7. Drive Level                           |                |       | 5   | mW    |

# **External Clock Drive Characteristics**

When driving the oscillator from an external clock source, XTAL2 must be left floating (unconnected). An external clock having the following characteristics must be used to ensure less than ±0.5 ns jitter at XMIT+/XMIT-.

| Clock Frequency: Rise/Fall Time (tR/tF): XTAL1 HIGH/LOW Time (tHIGH/tLOW): XTAL1 Falling Edge to Falling Edge Jitter: | 2-20 MHz +0.01%<br>< 2 ns from 0.8 V to 2.0 V<br>40 - 60% duty cycle<br>< +0.2 ns at 1.5 V input |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

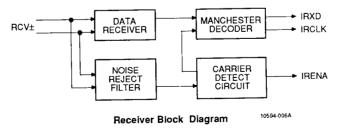

## Receiver Path

The principle functions of the Receiver are to signal the ILACC that there is information on the receive pair, and separate the incoming Manchester encoded data stream into clock and NRZ data.

The Receiver section (see Receiver Block Diagram)

consists of two parallel paths. The receive data path is a zero threshold, wide bandwidth line receiver. The carrier path is an offset threshold bandpass detecting line receiver. Both receivers share common bias networks to allow operation over a wide input common mode range.

Am79C900 1-65

## Input Signal Conditioning

Transient noise pulses at the input data stream are rejected by the Noise Rejection Filter. Pulse width rejection is proportional to transmit data rate. DC inputs more positive than minus 100 mV are also suppressed.

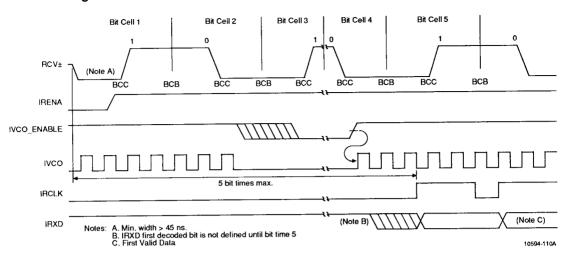

The Carrier Detection circuitry controls the stop and start of the phase-locked loop during clock acquisition. Clock acquisition requires a valid Manchester bit pattern of 1010 to lock onto the incoming message (see Receive Timing – Start of Reception Clock Acquisition waveform diagram).

When input amplitude and pulse width conditions are met at RCV+/RCV-, the internal enable signal from the SIA to controller (IRENA) is asserted and a clock acquisition cycle is initiated.

# **Clock Acquisition**

When there is no activity at RCV+/RCV- (receiver is idle), the receive oscillator is phase locked to ITCLK. The first negative clock transition after IRENA is asserted interrupts the receive oscillator. The oscillator is then restarted at the second Manchester "0" (bit time 4) and is phase locked to it. As a result, the SIA acquires the clock from the incoming Manchester bit pattern in 4 bit times with a "1010" Manchester bit pattern.

IRCLK and IRXD are enabled 1/4 bit time after clock acquisition in bit cell 5. IRXD, is at a HIGH state when the receiver is idle (no IRCLK). IRXD, however, is undefined when clock is acquired and may remain HIGH or change to LOW state whenever IRCLK is enabled. At 1/4 bit time through bit cell 5, the controller portion of the ILACC sees the first IRCLK transition. This also strobes in the incoming fifth bit to the SIA as Manchester "1". IRXD may make a transition after the IRCLK rising edge in bit cell 5, but its state is still undefined. The Manchester "1" at bit 5 is clocked to IRXD output at 1/4 bit time in bit cell 6.

# **PLL Tracking**

After clock acquisition, the phase-locked clock is compared to the incoming transition at BCC and the resulting phase error is applied to a correction circuit. This circuit ensures that phase-locked clock remains locked on the received signal. Individual bit cell phase corrections of the  $V_{\rm co}$  are limited to 100% of the phase difference between BCC and phase-locked clock. Hence, input data jitter is reduced in RCLK by 10 to 1.

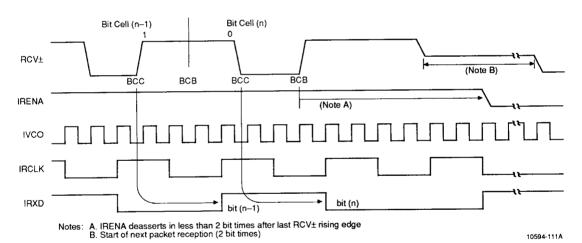

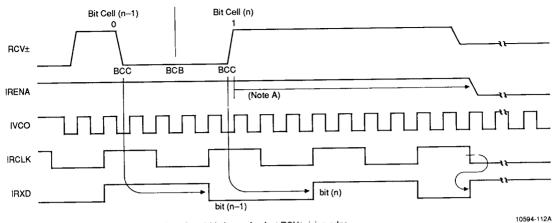

## Carrier Tracking and End of Message

The carrier detection circuit monitors the RCV+/RCV-inputs after IRENA is asserted for an end of message. IRENA deasserts 1 to 2 bit times after the last positive transition on the incoming message. This initiates the end of reception cycle. The time delay from the last rising edge of the message to IRENA deassert allows the last bit to be strobed by IRCLK and transferred to the controller section, but prevents any extra bit(s) at the end of message. When IRENA deasserts (see Receive Timing-End of Reception (Last Bit = 0) and Receive

Timing-End of Reception (Last Bit = 1) waveform diagrams) an IRENA hold off timer inhibits IRENA assertion for 1 to 2 bit times.

#### Data Decoding

The data receiver is a comparator with clocked output to minimize noise sensitivity to the RCV+/RCV- inputs. Input error is less than +/- 35 mV to minimize sensitivity to input rise and fall time. IRCLK strobes the data receiver output at 1/4 bit time to determine the value of the Manchester bit, and clocks the data out on IRXD on the following IRCLK. The data receiver also generates the signal used for phase detector comparison to the internal SIA voltage controlled oscillator (VCO).

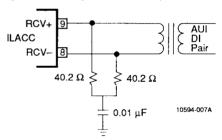

# **Differential Input Termination**

The differential input for the Manchester data (RCV+/RCV-) is externally terminated by two 40.2 ohm +1% resistors and one optional common-mode bypass capacitor, if direct coupling is used (as shown in the Differential Input Termination diagram below). The differential input impedance, Z<sub>IOF</sub>, and the common-mode input impendance, Z<sub>ICM</sub>, are specified so that the Ethernet specification for cable termination impedance is met using standard 1% resistor terminators. The COLL+/COLL- differential inputs are terminated in exactly the same way for the AUI DI pair.

**Differential Input Termination**

#### Collision Detection

A transceiver detects the collision condition on the network and generates a differential signal at the COLL+/COLL- inputs. This collision signal passes through an input stage which detects signal levels and pulse duration. When the signal is detected by the SIA it sets the ICLSN line HIGH. The condition continues for approximately 1.5 bit times after the last LOW-to-HIGH transition on COLL+/COLL-.

#### Jitter Tolerance Definition

The Receive Timing-Start of Reception Clock Acquisition waveform diagram shows the internal timing relationships implemented for decoding Manchester data in the SIA module. The SIA utilizes a clock capture circuit to align its internal data strobe with an incoming bit stream. The clock acquisition circuitry requires four valid bits with the values 1010. Clock is phase locked to the negative transition at the bit cell center of the second "0" in the pattern.

Since data is strobed at 1/4 bit time, Manchester transitions which shift from their nominal placement through 1/4 bit time will result in improperly decoded data. With this as the criteria for an error, a definition of "Jitter Handling" is:

The peak deviation approaching or crossing 1/4 bit cell position from nominal input transition, for which the SIA will properly decode data.

# **Data Flow Overview**

# DESCRIPTOR RING ACCESS MECHANISM - DETAILED DESCRIPTION

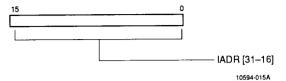

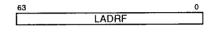

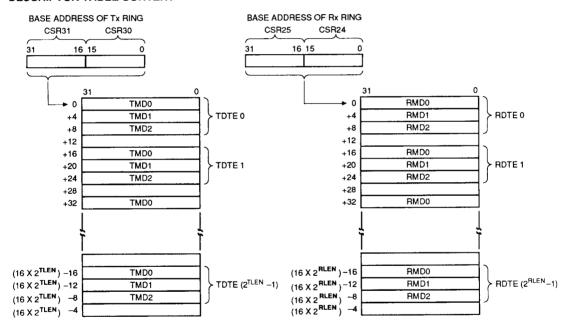

At initialization, the ILACC will have read the base address of both the transmit and receive descriptor rings. These will be stored in CSRs for use by the ILACC during subsequent operation (CSR24 = Base Address of Rx Ring, CSR30 = Base Address of Tx Ring).

With the ILACC started, and the transmit and receive functions enabled, the base address of each ring will be loaded into the current descriptor address registers (CSR28 = Current Address of Rx Ring, CSR34 = Current Address of Tx Ring).

The address of the next descriptor in the transmit and receive rings will be computed (current ring address + descriptor table entry length) and loaded into CSR26 (Next Address of Rx Ring) and CSR32 (Next Address of Tx Ring).

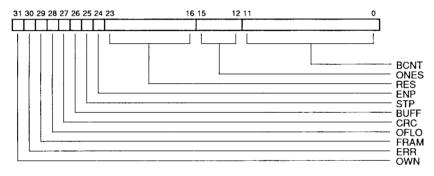

## TRANSMIT DESCRIPTOR TABLE ENTRY (TDTE)

When there is no channel activity, the ILACC will use the current descriptor address stored internally, to vector to the appropriate TDTE. It will subsequently poll the entry, awaiting the host to set the OWN bit (in TMD1). This will be set by the host to signal that a buffer has been queued for transmission. The poll time is a function of BCLK. The descriptor will be polled at intervals of  $32.768 \times T_{\rm RCLK}$  (BCLK period).

If the OWN and start of packet (STP) bits are set, the ILACC will save the status bits, and any address information within TMD1, and subsequently read TMD0 to obtain the full address of the data buffer. This will be saved in the Current Tx Buffer Address (CSR20) location. The length field will be read from TMD1 and saved in the Current Tx Byte Count (CSR42) location. Each of these memory reads is performed separately with a new arbitration cycle for each transfer.

If the OWN bit was set, but STP = 0, the ILACC will reset the OWN bit and move to the next transmit descriptor in the ring.

If the transmit buffers are data chained (ENP = 0), the ILACC will look ahead to the next transmit descriptor in the ring, before transferring the first data burst for the current data buffer to the FIFO. This lookahead operation is performed only once.

If the ILACC does not own the next TDTE (i.e., the second TDTE for this packet), it will complete transmission of the current buffer, and update the status of the current (tirst) TDTE by setting the BUFF bit. This will cause the transmitter to be disabled (CSR0, TXON = 0). The ILACC will have to be re-initialized to restore the transmit function.

If the ILACC owns the second TDTE, it will also read the buffer address and byte count entries. The information read from the next buffer in the chain is saved by the ILACC in the Next Rx/Tx Buffer Address (CSR22), the Next Rx/Tx Byte Count (CSR44), and the Next Rx/Tx Status (CSR54) locations. Once the ILACC has completed emptying the current buffer, it will clear the OWN bit, overwrite all "current" descriptor and buffer entries with "next" entries in the appropriate CSR locations, and immediately start loading data from the second buffer.

Between DMA bursts, starting from the second buffer, the ILACC again performs the lookahead operation, to check for ownership of the next (third) buffer. This sequence will continue, until a TDTE indicates the end of the packet (ENP =1). When all data from the packet has been transmitted from the FIFO to the channel, the ILACC will update the status bits in TMD1 and write the Transmit Collision Count (TMD2). If there were errors, TMD2 will be updated, prior to the ILACC relinquishing ownership of the last buffer. The ILACC will subsequently inspect the next buffer for ownership (first buffer in next packet), to guarantee back-to-back packet transmission.

If the next buffer is not owned by the ILACC, then it will continue to poll the TDTE every 1.6ms (BCLK = 20 MHz), until the host toggles the state of the OWN bit.

If an error occurs before all buffers are transmitted (i.e., RTRY or LCOL), the ILACC will stop the current packet transmission, reset the OWN bit in TMD1, and set the TINT bit in CSR0, causing an interrupt if IENA = 1. The ILACC will not transmit the remaining buffer(s) in the packet. Instead, it will reset the OWN bit and update the error flags (TMD2) in the current TDTE. The ILACC will subsequently reset the OWN bit in each TDTE it polls, until it locates a TDTE with both OWN and STP set, indicating the first buffer of a new packet.

When the transmit buffers are not chained (ENP = 1), indicating a single buffer packet or the last buffer in a multi-buffer packet, the ILACC does not perform the lookahead operation. It will transmit the current buffer, update TMD2 if an error occurred, update the status and reset the OWN bit in TMD1, and overwrite CSR34 (Current Address of Tx Ring) with the contents of CSR32 (Next Address of Tx Ring). The ILACC will then immediately check the current TDTE for ownership. If the ILACC owns the descriptor, it will read the other entries in the descriptor table, and save them in the "current" data buffer locations. Transfer of the data to

the FIFO for transmission, lookahead operation and update of the CSR locations will then follow the sequence as described. If the ILACC does not own the descriptor, it will poll the descriptor entry every 1.6ms (BCLK = 20MHz) until the host toggles the state of the OWN bit. The host may set the TDMD bit in CSR0 once it has passed ownership of the buffer to the ILACC. This will force the ILACC to check the OWN bit of the "current" TDTE, without waiting for the poll time to elapse.

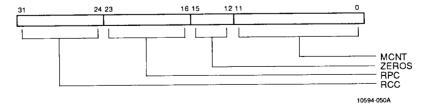

# RECEIVE DESCRIPTOR TABLE ENTRY (RDTE)

Receive ring access is similar to that of the transmit ring. Once the receiver is enabled, the ILACC will check for ownership of the receive descriptor designated as "current" (as defined in the Current Rx Buffer Address in CSR18). With no incoming messages, and the OWN bit clear, the ILACC will poll RMD1 every 1.6ms (BCLK = 20MHz) until the host relinquishes ownership. Once the ILACC owns the buffer, it will read the buffer address and length, updating the "current" CSR entries.

When a packet is received from the channel, the ILACC will first check that it owns a receive buffer. If it does not, it will poll the receive descriptor once more to determine if the host has relinquished ownership. If ownership remains with the host, the ILACC has no receive buffer in which to dump the incoming packet data. It will set the MISS error in CSR0 (generating an interrupt if INEA is set), and will not poll the RDTE until the packet has completed.

If the ILACC owns a receive buffer when a packet is received, it will interleave a lookahead operation while dumping the receive data into the buffer. This lookahead operation will consist of a single DMA read of the next RDTE status (RMD1), if ownership of the buffer remains with the host. If the OWN bit is set, the lookahead will consist of two separate DMA read operations, as the address and length fields of the buffer are also read from the DTE. The "next" fields in the CSR locations will be updated with the information from the lookahead. Either lookahead operation is performed only once.

Regardless of ownership of the second receive buffer, the ILACC will complete the received data transfer from the FIFO to the first receive buffer, under burst-mode DMA.

If the packet length exceeds the length of the first buffer and requires buffer chaining, and the ILACC does not own the second buffer, it will update the current descriptor status in RMD1 with the BUFF and possibly OFLO bits set, toggle the OWN bit, and overwrite the Current Address of Rx Ring (CSR28) with the Next Address of Receive Ring (CSR26). If the ILACC does own the second buffer, it will relinquish the current buffer, overwrite all "current" descriptor and buffer entries in CSRs

with "next" entries (as read in the previous lookahead), and commence unloading the FIFO to the second buffer in the chain. Between DMA bursts to unload the FIFO, the ILACC will perform the next lookahead operation to check for ownership of the next (third) RDTE. If it does own the descriptor, it will again read the address and length fields and update the "next" buffer locations in the appropriate CSRs.

This activity continues until the ILACC recognizes the completion of the packet (channel becomes idle). The ILACC will subsequently update the current RDTE status with the end of packet (ENP) indication set, write the message byte count (MCNT) for the complete packet into RMD2, and overwrite the "current" entries in the CSRs with the "next" entries.

If after receive completion, the packet is detected as a runt, the "current" buffer address and status in the RDTE are not updated, and the internal CSRs are also not updated. The runt packet data buffer will be overwritten by the next received message data.

At this stage, dependent on ownership during the previous lookahead operation, the "next" CSR locations associated with the data buffer status, address and length, may or may not contain the next data buffer to be used. The "current" CSR locations associated with the RDTE will contain the information necessary to poll the next descriptor in the ring if necessary.

# SERIAL TRANSMISSION

Serial transmission consists of sending an unbroken bit stream from either the TxD output or XMIT+/XMIT- pair consisting of:

- Preamble/Start Frame Delimeter (SFD): 56 bits (7 bytes) of alternating ONES and ZEROES terminating with the 8-bit (1-byte) SFD sequence of 10101011.

- Data: The serialized byte stream from the FIFO shifted out with the LSB first.

- CRC: The inverted 32-bit polynomial calculated from the data, address, and type fields, shifted out with the MSB first. The CRC is not transmitted if:

- Transmission of the data field is truncated for any reason.

- b. CDT or COLL+/- becomes active at any time during transmission.

- c. DTCR = 1 (CSR15, bit 03) in a normal or loopback transmission mode.

The transmission is indicated at the general purpose serial interface by the assertion of RTS with the first bit of the preamble and the negation of RTS after the last transmitted bit.

The ILACC starts transmitting the preamble when the following are satisfied:

- 1. There is at least 1 byte of data to be transmitted in the FIFO.

- 2. The interpacket gap time (IPG) has elapsed.

- The backoff interval has elapsed, if a retransmission is required.

#### SERIAL RECEPTION

Serial reception consists of receiving an unbroken bit stream on the RxD input or RCV+/RCV- pair consisting of: