# Intelligent GPIB Interface Controller

#### PIN CONFIGURATION **FEATURES** □ All Functional Interface Capability Meeting IEEE Standard 488-1978 -SH1 (Source Handshake) -AH1 (Acceptor Handshake) T/B 1 1 [ 40 V<sub>CC</sub> -T5 or TE5 (Talker or Extended Talker) T/R2 20 39 EO1 38 NDAC -L3 or LE3 (Listener or Extended Listener) CLOCK 3 C 37 NRFD RESET -SR1 (Service Request) T/R3 5 D -RL1 (Remote Local) 35 DIO 8 DMAREQ 7 n b 34 DIO 7 -PP1 or PP2 (Parallel Poll) (Remote or Local DMAACK h 33 DIO 6 Configuration) RD 9 0 32 DIO 5 -DC1 (Device Clear) 31 DIO 4 WR 10 d INT 11 C 30 DIO 3 -DT1 (Device Trigger) D0 12 d 29 DIO 2 -C1-5 ((Controller) (All Functions)) D1 13 d 28 DIO 1 □ Programmable Data Transfer Rate D2 14 0 27 SRQ ☐ 16 MPU Accessible Registers—8 Read/8 Write 26 ATN D3 15 C D4 16 D D5 17 D 25 REN □ 2 Address Registers —Detection of MTA, MLA, MSA (My Talk/Listen/ b 23 BS 2 D6 18 C Secondary Address) 22 RS 1 D7 19 C GND 20 [ 21 RS 0 –2 Device Addresses ☐ EOS Message Automatic Detection PACKAGE: 40-pin D.I.P. Command (IEEE Standard 488-78) Automatic Processing and Undefined Command Read Capability DMA Capability □ COPLAMOS®n-Channel Silicon Gate Technology ☐ Programmable Bus Transceiver I/O Specification (Works with T.I./Motorola/Intel) ☐ +5V Single Power Supply 40-Pin DIP ☐ 1 to 8 MHz Clock Range

#### **GENERAL DESCRIPTION**

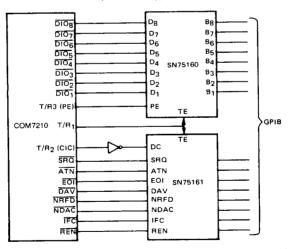

The COM7210 TLC is an intelligent GPIB Interface Controller designed to meet all of the functional requirements for Talkers, Listeners, and Controllers as specified by the IEEE Standard 488-1978. Connected between a processor bus and the GPIB, the TLC provides high level manage-

TTL Compatible

ment of the GPIB to unburden the processor and to simplify both hardware and software design. Fully compatible with most processor architectures, Bus Driver/Receivers are the only additional components required to implement any type of GPIB interface.

■ 8080/85/86 Compatible

#### **DESCRIPTION OF PIN FUNCTIONS**

| PIN   | SYMBOL          | I/O | DESCRIPTION                                                                                                                                                                |

|-------|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | T/R1            | 0   | Transmit/Receive Control—Input/Output Control Signal for the GPIB Bus Transceivers.                                                                                        |

| 2     | T/R2            | 0   | Transmit/Receive Control—The functions of T/R2, T/R3 are determined by the values of TRM1, TRM0 of the address mode register.                                              |

| 3     | CLK             | I   | Clock—(1-8 MHz) Reference Clock for generating the state change prohibit times T1, T6, T7, T9 specified in IEEE Standard 488-1978.                                         |

| 4     | RST             |     | Reset—Resets 7210 to an idle state when high (active high).                                                                                                                |

| 5     | T/R3            | 0   | Transmit/Receive Control—Function determined by TRM1 and TRM0 of address mode register (See T/R2).                                                                         |

| 6     | DMAREQ          | 0   | DMA Request—7210 requests data transfer to the computer system becomes low on input of DMA acknowledge signal DACK.                                                        |

| 7     | DMAACK          | 1   | DMA Acknowledge—(Active Low) Signal connects the computer system data bus to the data register of the 7210.                                                                |

| 8     | CS              | ı   | Chip Select—(Active Low) Enables access to the register selected by RS0-2 (read or write operation).                                                                       |

| 9     | RD              | 1   | Read—(Active Low) Places contents of read register specified by RS0-2—on D0-7 (Computer Bus).                                                                              |

| 10    | WR              | I   | Write—(Active Low) writes data on D0-7 into the write register specified by RS0-2.                                                                                         |

| 11    | INT INT         | 0   | Interrupt Request—(Active High/Low) Becomes active due to any 1 of 13 internal interrupt factors (unmasked) active state software configurable, active high on chip reset. |

| 12-19 | D0-7            | 1/0 | Data Bus—8-bit bidirectional data bus, for interface to computer system.                                                                                                   |

| 20    | GND             |     | Ground.                                                                                                                                                                    |

| 21-23 | RS0-2           | I   | Register Select—These lines select one of eight read (write) registers during a read (write) operation.                                                                    |

| 24    | ĪFC             | I/O | Interface Clear—Control line used for clearing the interface functions.                                                                                                    |

| 25    | REN             | 1/0 | Remote Enable—Control line used to select remote or local control of the devices.                                                                                          |

| 26    | ĀTN             | 1/0 | Attention—Control line which indicates whether data on DIO lines is an interface message or device dependent message.                                                      |

| 27    | SRQ             | 1.0 | Service Request—Control line used to request the controller for service.                                                                                                   |

| 28-35 | DIO1-8          | I:O | Data Input/Output—8-bit bidirectional bus for transfer of message on the GPIB.                                                                                             |

| 36    | DAV             | 1/0 | Data Valid—Handshake line indicating that data on DIO lines is valid.                                                                                                      |

| 37    | NRFD            | 1/0 | Ready for Data—Handshake line indicating that device is ready for data.                                                                                                    |

| 38    | NDAC            | 1/0 | Data Accepted—Handshake line indicating completion of message reception.                                                                                                   |

| 39    | EOI             | 1/0 | End or Identify—Control line used to indicate the end of multiple byte transfer sequence or to execute a parallel polling in conjunction with ATN.                         |

| 40    | V <sub>cc</sub> |     | +5V DC                                                                                                                                                                     |

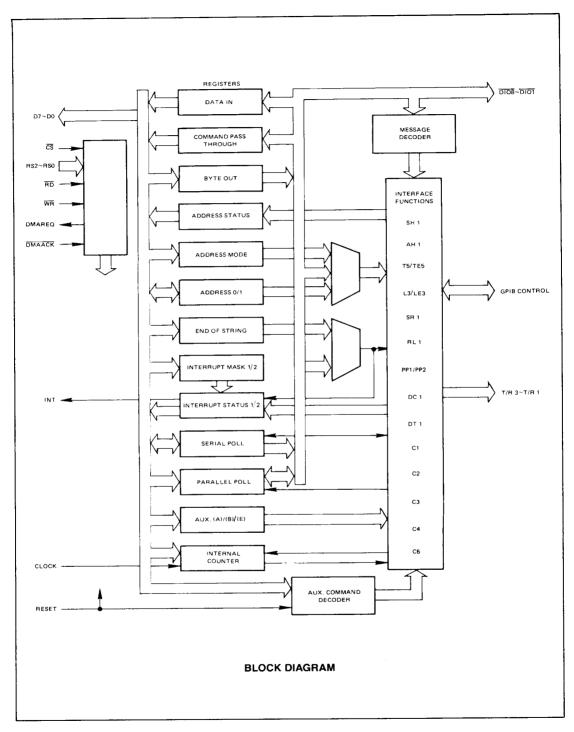

#### **FUNCTIONAL DESCRIPTION**

#### Introduction

The IEEE Standard 488 describes a "Standard Digital Interface for Programmable Instrumentation" which, since its introduction in 1975, has become the most popular means of interconnecting instruments and controllers in laboratory, automatic test and even industrial applications. Refined over several years, the 488-1978 Standard, also known as the General Purpose Interface Bus (GPIB), is a highly sophisticated standard providing a high degree of flexibility to meet virtually most all instrumentation requirements. The COM7210 TLC implements all of the functions that are required to interface to the GPIB. While it is beyond the scope of this document to provide a complete explanation of the IEEE 488 Standard, a basic description follows:

The GPIB interconnects up to 15 devices over a common set of data control lines. Three types of devices are defined by the standard: Talkers, Listeners, and Controllers, although some devices may combine functions such as Talker/Listener or Talker/Controller.

Data on the GPIB is transferred in a bit parallel, byte serial fashion over 8 Data I/O lines (D101-D108). A 3 wire handshake is used to ensure synchronization of transmission and reception. In order to permit more than one device to receive data at the same time, these control lines are "Open Collector" so that the slowest device controls the data rate. A number of other control lines perform a variety of functions such as device addressing, interrupt generation, etc.

The COM7210 TLC implements all functional aspects of Talker, Listener and Controller functions as defined by the 488-1978 Standard, and on a single chip.

The COM7210 TLC is an intelligent controller designed to provide high level protocol management of the GPIB, freeing the host processor for other tasks. Control of the TLC is accomplished via 16 internal registers. Data may be transferred either under program control or via DMA using the TLC's DMA control facilities to further reduce processor

overhead. The processor interface of the TLC is general in nature and may be readily interfaced to most processor lines.

In addition to providing all control and data lines necessary for a complete GPIB implementation, the TLC also provides a unique set of bus transceiver controls permitting the

use of a variety of different transceiver configurations for maximum flexibility.

#### **Internal Registers**

The TLC has 16 registers, 8 of which are read and 8 write.

| REGISTER NAME             | 1           | \D[         | RE          | SS     | INC    | <b>3</b> |      | ** * |      | SPECIFI | CATION |       |       |       |

|---------------------------|-------------|-------------|-------------|--------|--------|----------|------|------|------|---------|--------|-------|-------|-------|

|                           | R<br>S<br>2 | R<br>S<br>1 | R<br>S<br>0 | W<br>R | R<br>D | C<br>S   |      |      |      |         |        |       |       |       |

| Data In (0R)              | 0           | 0           | 0           | 1      | 0      | 0        | D17  | D16  | D15  | D14     | D13    | D12   | D11   | D10   |

| Interrupt Status 1 (1R)   | 0           | 0           | 1           | 1      | 0      | 0        | CPT  | APT  | DET  | END     | DEC    | ERR   | D0    | D1    |

| Interrupt Status 2 (2R)   | 0           | 1           | 0           | 1      | 0      | 0        | INT  | SRQ1 | LOK  | REM     | CO     | LOKC  | REMC  | ADSC  |

| Serial Poll Status (3R)   | 0           | 1           | 1           | 1      | 0      | 0        | S8   | PEND | S6   | S5      | S4     | S3    | S2    | S1    |

| Address Status (4R)       | 1           | 0           | 0           | 1      | 0      | 0        | CIC  | ATN  | SPMS | LPAS    | TPAS   | LA    | TA    | MJMN  |

| Command Pass Through (5R) | 1           | 0           | 1           | 1      | 0      | 0        | CPT7 | CPT6 | CPT5 | CPT4    | CPT3   | CPT2  | CPT1  | CPT0  |

| Address 0 (6R)            | 1           | 1           | 0           | 1      | 0      | 0        | X    | DT0  | DL0  | AD5-0   | AD4-0  | AD3-0 | AD2-0 | AD1-0 |

| Address 1 (7R)            | 1           | 1           | 1           | 1      | 0      | 0        | EO1  | DT1  | DL1  | AD5-1   | AD4-1  | AD3-1 | AD2-1 | AD1-1 |

| Byte Out (0W)             | 0           | 0           | 0           | 0      | 1      | 0        | BO7  | BO6  | BO5  | BO4     | ВО3    | BO2   | BO1   | BO0   |

| Interrupt Mask 1 (1W)     | 0           | 0           | 1           | 0      | 1      | 0        | CPT  | APT  | DET  | END     | DEC    | ERR   | DO    | DI    |

| Interrupt Mask 2 (2W)     | 0           | 1           | 0           | 0      | 1      | 0        | 0    | SRQI | DMAO | DMAI    | co     | LOKC  | REMC  | ADSC  |

| Serial Poll Mode (3W)     | 0           | 1           | 1           | 0      | 1      | 0        | S8   | rsv  | S6   | S5      | S4     | S3    | S2    | S1    |

| Address Mode (4W)         | 1           | 0           | 0           | 0      | 1      | 0        | ton  | lon  | TRM1 | TRM0    | 0      | 0     | ADM1  | ADM0  |

| Auxiliary Mode (5W)       | 1           | 0           | 1           | 0      | 1      | 0        | CNT2 | CNT1 | CNT0 | СОМ4    | сомз   | COM2  | COM1  | СОМО  |

| Address 0/1 (6W)          | 1           | 1           | 0           | 0      | 1      | 0        | ARS  | DT   | DL   | AD5     | AD4    | AD3   | AD2   | AD1   |

| End of String (7W)        | 1           | 1           | 1           | 0      | 1      | 0        | EC7  | EC6  | EC5  | EC4     | EC3    | EC2   | EC1   | EC0   |

#### **Data Registers**

The data registers are used for data and command transfers between the GPIB and the microcomputer system.

| DATA IN (0R)                                  | DI7 | DI6 | DI5 | DI4 | DI3 | DI2 | DI1 | DI0 |  |  |

|-----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|--|--|

| Holds data sent from the GPIB to the computer |     |     |     |     |     |     |     |     |  |  |

| BYTE OUT (0W)                                 | BO7 | BO6 | BO5 | BO4 | воз | BO2 | BO1 | BO0 |  |  |

Holds information written into it for transfer to the GPIB

#### **Interrupt Registers**

The interrupt registers are composed of interrupt status bits, interrupt mask bits, and some other noninterrupt related bits.

| W. T. C. C. L. C. T.        | READ  |      |     |     |     |      |      |      |  |

|-----------------------------|-------|------|-----|-----|-----|------|------|------|--|

| INTERRUPT<br>STATUS 1 (1R). | CPT   | APT  | DET | END | DEC | ERR  | DO   | DI   |  |

| INTERRUPT<br>STATUS 2 (2R)  | INT   | SRQI | LOK | REM | СО  | LOKC | REMC | ADSC |  |

|                             | WRITE |      |     |     |     |      |      |      |  |

| INTERRIBE                   |       |      |     | WR  | ITE |      |      |      |  |

| INTERRUPT<br>MASK 1 (1W)    | CPT   | APT  | DET | END | DEC | ERR  | DO   | DI   |  |

#### Interrupt Status Bits

| OR of All Unmasked Interrupt Status Bits |

|------------------------------------------|

| Command Pass Through                     |

| Address Pass Through                     |

| Device Trigger                           |

| End (END or EOS Message Received)        |

| Device Clear                             |

| Error                                    |

| Data Out                                 |

| Data In                                  |

| Service Request Input                    |

| Lockout Change                           |

| Remote Change                            |

| Address Status Change                    |

| Command Output                           |

|                                          |

There are thirteen factors which can generate an interrupt from the COM7210, each with their own status bit and mask bit.

The interrupt status bits are always set to one if the interrupt condition is met. The interrupt mask bits decide whether the INT bit and the interrupt pin will be active for that condition.

#### Noninterrupt Related Bits

| LOK  | Lockout                |  |

|------|------------------------|--|

| REM  | Remote/Local           |  |

| DMAO | Enable/Disable DMA Out |  |

| DMAI | Enable/Disable DMA In  |  |

#### Serial Poll Registers

|                            |    |      |    | HE   | :AD  |    |    |    |

|----------------------------|----|------|----|------|------|----|----|----|

| SERIAL POLL<br>STATUS (3R) | S8 | PEND | S6 | S5   | S4   | S3 | S1 | S0 |

|                            |    |      | ·  | \A/E | RITE |    |    |    |

| OFRIAL BOLL                |    |      |    | VV I | 1116 |    |    |    |

| SERIAL POLL<br>MODE (3W)   | S8 | rsv  | S6 | S5   | S4   | S3 | S2 | S1 |

The Serial Poll Mode register holds the STB (status byte: S8, S6-S1) sent over the GPIB and the local message rsv (request service). The Serial Poll Mode register may be read through the Serial Poll Status register. The PEND is set by rsv = 1, and cleared by NPRS •  $\vec{rsv}$  = 1 (NPRS = Negative Poll Response State).

#### Address Mode/Status Registers

| ADDRESS STATUS (4R) | CIC | ATN | SPMS | LPAS | TPAS | LA | TA   | MJMN |

|---------------------|-----|-----|------|------|------|----|------|------|

|                     |     |     |      |      |      |    |      |      |

| ADDRESS MODE (4W)   | ton | Ion | TRM1 | TRM0 | 0    | 0  | ADM1 | ADM0 |

The Address Mode register selects the address mode of the device and also sets the mode for T/R3 and T/R2 the transceiver control lines.

The functions of T/R2, T/R3 terminals (2 and 5) are determined as below by the TRM1, TRM0 values of the address mode register.

| T/R2  | T/R3  | TRM1 | TRM0 |

|-------|-------|------|------|

| EOIOE | TRIG  | 0    | 0    |

| CIC   | TRIG  | 0    | 1    |

| CIC   | EOIOE | 1    | 0    |

| CIC   | PE    | 11   | 1    |

EOIOE = TACS + SPAS + CIC • CSBS

This denotes the input/output of EOI terminal.

When "1": Output When "0": Input  $CIC = \overline{CIDS} + \overline{CADS}$

This denotes if the controller interface function is active or

When "1":  $\overline{ATN} = \text{output}$ ,  $\overline{SRQ} = \text{input}$  When "0":  $\overline{ATN} = \text{input}$ ,  $\overline{SRQ} = \text{output}$

PE = CIC + PPAS

This indicates the type of bus driver connected to DI08 to DI01 and DAV lines.

When "1": 3 state type When "0": Open collector type

TRIG: When DTAS state is initiated or when a trigger auxiliary command is issued, a high pulse is generated.

Upon RESET, TRM0 and TRM1 become "0" (TRM0 = TRM1 = 0) and local message port is provided, so that T/R2 and T/R3 both become "LOW."

#### Address Modes

| ton | lon       | ADM1      | ADM0        | ADDRESS<br>MODE      | CONTENTS OF<br>ADDRESS (0)<br>REGISTER                                          | CONTENTS OF<br>ADDRESS (1)<br>REGISTER        |                                     |                                    |

|-----|-----------|-----------|-------------|----------------------|---------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------|------------------------------------|

| 1   | 0         | 0         | 0           | Talk only<br>mode    | Address Identification Not Necessary<br>(No controller on the GPIB)<br>Not Used |                                               |                                     |                                    |

| 0   | 1         | 0         | 0           | Listen only<br>mode  |                                                                                 |                                               |                                     |                                    |

| 0   | 0         | 0         | 1           | Address mode 1       | Major talk address or<br>Major listen address                                   | Minor talk address or<br>Minor listen address |                                     |                                    |

| 0   | 0 0 1     |           | 0 1 0       |                      | 0                                                                               | Address mode 2                                | Primary address<br>(talk or listen) | Secondary address (talk or listen) |

| 0   | 0         | 1         | . 1         | Address mode 3       | Primary address (major talk or major listen)                                    | Primary address (minor talk or minor listen)  |                                     |                                    |

| Com | binations | other tha | in above ir | ndicated Prohibited. |                                                                                 |                                               |                                     |                                    |

Notes: (A1)

-Either MTA or MLA reception is indicated by coincidence of either address with the received address. Interface function T or L.

(A2)

**SPMS**

-Address register 0 = primary, Address register 1 = secondary, interface function TE or LE.

(A3) -CPU must read secondary address via Command Pass Through Register interface function (TE or LE).

#### Address Status Bits

ATN Data Transfer Cycle (device in CSBS) **LPAS**

Listener Primary Addressed State Talker Primary Addressed State TPAS

CIC LA Listener Addressed

Controller Active

Talker Addressed

M.IMN Sets minor T/L address Reset = Major T/L

address

Serial Poll Mode State

#### **Address Registers**

| ADDRESS 0 (6R)   | X   | DT0 | DL0 | AD5-0 | AD4-0 | AD3-0 | AD2-0 | AD1-0 |

|------------------|-----|-----|-----|-------|-------|-------|-------|-------|

| ADDRESS 1 (7R)   | EOI | DT1 | DL1 | AD5-1 | AD4-1 | AD3-1 | AD2-1 | AD1-1 |

| ADDRESS 0/1 (6W) | ARS | DT  | DL  | AD5   | AD4   | AD3   | AD2   | AD1   |

The TLC is able to automatically detect two types of addresses which are held in address registers 0 and 1. The addressing modes are outlined below.

Address settings are made by writing into the address 0/1 register. The function of each bit is described below.

#### Address 0/1 Register Bit Selections

-Selects which address register, 0 or 1 ARS AD5-AD1 —Device address value

DT Holds the value of EOI line when data is Permits or Prohibits address to be detected EOI received

as Talk DL Permits or Prohibits address to be detected

as Listen

#### Command Pass Through Register

| COMMAND PASS |      |      |      |      |      |      |     |      |

|--------------|------|------|------|------|------|------|-----|------|

| THROUGH (5R) | CPT7 | CPT6 | CPT5 | CPT4 | CPT3 | CPT2 | CP1 | CPT0 |

The CPT register is used such that the CPU may read the address, or parallel poll response. DIO lines in the cases of undefined command, secondary

#### **End of String Register**

| END OF      |     |     |     |     |     |     |     |     |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| STRING (7W) | EC7 | EC6 | EC5 | EC4 | EC3 | EC2 | EC1 | EC0 |

This register holds either a 7- or 8-bit EOS message byte used in the GPIB system to detect the end of a data block.

Aux Mode Register A controls the specific use of this register.

#### Auxiliary Mode Register

**AUXILIARY** CNTO COM4 COM3 COM2 COM1 COM0 MODE (5W) CNT2 CNT1

This is a multipurpose register. A write to this register generates one of the following operations according to the values of the CNT bits.

| 70 | CN1 | r<br>o | _              |                | OI<br>2        |    | 0              | OPERATION                                                                                                |  |  |  |  |  |

|----|-----|--------|----------------|----------------|----------------|----|----------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0  | 0   |        | C <sub>4</sub> | _              |                |    | Ť              | Issues an auxiliary command specified by C <sub>4</sub> to C <sub>6</sub> .                              |  |  |  |  |  |

| 0  | 0   | 1      | 0              | F <sub>3</sub> | F <sub>2</sub> | F, | F <sub>o</sub> | The reference clock frequency is specified and $T_1$ , $T_6$ , $T_7$ , $T_9$ are determined as a result. |  |  |  |  |  |

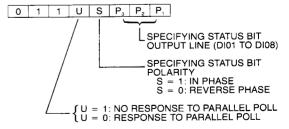

| 0  | 1   | 1      | υ              | S              | P <sub>3</sub> | P  | P,             | Makes write operation to the parallel poll register.                                                     |  |  |  |  |  |

| 1  | 0   | 0      | Α₄             | A <sub>3</sub> | A <sub>2</sub> | Α, | Ao             | Makes write operation to the aux. (A) register.                                                          |  |  |  |  |  |

| 1  | 0   | 1      | В₄             | Вз             | B <sub>2</sub> | В, | Во             | Makes write operation to the aux. (B) register.                                                          |  |  |  |  |  |

| 1  | 1   | 0      | 0              | 0              | 0              | Ε, | Eo             | Makes write operation to the aux.<br>(E) register.                                                       |  |  |  |  |  |

| Auxiliary C                               | ommands                           | 0 0 0 C <sub>4</sub> C <sub>3</sub> C <sub>2</sub> C <sub>1</sub> C <sub>0</sub>                             |

|-------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------|

| 43210<br>00000                            | iepon                             | Immediate Execute pon<br>Generate local pon<br>Message                                                       |

| 00010                                     | crst                              | Chip Reset-Same as<br>External Reset                                                                         |

| 00011<br>00100<br>00101                   | rrfd<br>trig<br>rtl               | <ul> <li>Release RFD</li> <li>Trigger</li> <li>Return to Local Message<br/>Generation</li> </ul>             |

| 00110<br>00111                            | seoi<br>nvid                      | <ul> <li>Send EOI Message</li> <li>Non Valid (OSA reception)—</li> <li>Release DAC Holdoff</li> </ul>        |

| 01111                                     | vid                               | Valid (MSA reception, CPT, DEC, DET)—Release DAC Holdoff                                                     |

| 0X001<br>10000<br>10001                   | sppf<br>gts<br>tca                | <ul> <li>Set/Reset Parallel Poll Flag</li> <li>Go To Standby</li> <li>Take Control Asynchronously</li> </ul> |

| 10010<br>11010                            | tcs<br>tcse                       | Take Control Synchronously     Take Control Synchronously     on End                                         |

| 10011<br>11011                            | Itn<br>Itnc                       | <ul><li>Listen</li><li>Listen with Continuous</li><li>Mode</li></ul>                                         |

| 11100<br>11101<br>1X110<br>1X111<br>10100 | lun<br>epp<br>sifc<br>sren<br>dsc | Local Unlisten     Execute Parallel Poll     Set/Reset IFC     Set/Reset REN     Disable System Control      |

#### Internal Counter 0 0 1 0 F<sub>3</sub> F<sub>2</sub> F<sub>1</sub> F<sub>0</sub>

The internal counter generates the state change prohibit times  $(T_1, T_6, T_7, T_9)$  specified in the IEEE std 488-1978 with reference to the clock frequency.

# Auxiliary A Register 1 0 0 $A_4$ $A_3$ $A_2$ $A_1$ $A_0$

Of the 5 bits that may be specified as part of its access word, 2 bits control the GPIB data receiving modes of the 7210 and 3 bits control how the EOS message is used.

| A, | A <sub>o</sub> | DATA RECEIVING MODE           |

|----|----------------|-------------------------------|

| 0  | 0              | Normal Handshake Mode         |

| 0  | 1              | RFD Holdoff on all Data Modes |

| 1  | 0              | RFD Holdoff on End Mode       |

| 1  | 1              | Continuous Mode               |

| BIT<br>NAME           |   |           | FUNCTION                                                                          |

|-----------------------|---|-----------|-----------------------------------------------------------------------------------|

| ^                     | 0 | Prohibit  | Permits (prohibits) the setting of the END bit by reception of the                |

| Α₂                    | 1 | Permit    | EOS message.                                                                      |

| ^                     | 0 | Prohibit  | Permits (prohibits) automatic transmission of END message simultaneously with the |

| <b>Α</b> <sub>3</sub> | 1 | Permit    | transmission of EOS message<br>TACS.                                              |

| <b>A</b> <sub>4</sub> | 0 | 7 bit EOS | Makes the 8 bits/7 bits of EOS                                                    |

|                       | 1 | 8 bit EOS | register the valid EOS message.                                                   |

# Auxiliary B Register 1 0 1 B<sub>4</sub> B<sub>3</sub> B<sub>2</sub> B<sub>1</sub> B<sub>0</sub>

The Auxiliary B Register is much like the A Register in that it controls the special operating features of the device.

| BIT            |          | · · · · · · · · · · · · · · · · · · · | FUNCTION                                                                                                                                |  |  |  |  |  |

|----------------|----------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME           |          |                                       |                                                                                                                                         |  |  |  |  |  |

| B <sub>o</sub> | 1 Permit |                                       | Permits (prohibits) the detection of undefined command. In other words, it permits (prohibits)                                          |  |  |  |  |  |

| J.,            | 0        | Prohibit                              | the setting of the CPT bit on reception of an undefined command.                                                                        |  |  |  |  |  |

|                | 1 Permit |                                       | Permits (prohibits) the<br>transmission of the END                                                                                      |  |  |  |  |  |

| В,             | 0        | Prohibit                              | message when in serial poll active state (SPAS).                                                                                        |  |  |  |  |  |

|                | 1        | T,<br>(high-speed)                    | T, (high speed) as T, of<br>handshake after transmission of<br>2nd byte following data<br>transmission.                                 |  |  |  |  |  |

| B <sub>2</sub> | 0        | T, (low-speed)                        |                                                                                                                                         |  |  |  |  |  |

|                | 1        | INT                                   | Specifies the active level of INT pin.                                                                                                  |  |  |  |  |  |

| B₃             | 0        | INT                                   |                                                                                                                                         |  |  |  |  |  |

| B <sub>4</sub> | 1        | ist = SRQS                            | SRQS indicates the value of ist level local message (the value of the parallel poll flag is ignored). SRQS = 1ist = 1. SRQS = 0ist = 0. |  |  |  |  |  |

|                | 0        | ist = Parallel<br>Poll Flag           | The value of the parallel poll flag is taken as the ist local message.                                                                  |  |  |  |  |  |

# Auxiliary E Register 1 1 0 0 0 0 E<sub>1</sub> E<sub>0</sub>

This register controls the Data Acceptance Modes of the TLC.

| BIT            |     | FUNCTION |                                   |  |  |  |  |  |  |  |

|----------------|-----|----------|-----------------------------------|--|--|--|--|--|--|--|

| _              | 1   | Enable   | DAC Holdoff by initiation of DCAS |  |  |  |  |  |  |  |

| E <sub>o</sub> | 0   | Disable  | DAC Holdon by initiation of Beat  |  |  |  |  |  |  |  |

| _              | _ 1 |          | DAC Holdoff by initiation of DTAS |  |  |  |  |  |  |  |

| E,             | 0   | Disable  | DAC Holden by initiation of DTAS  |  |  |  |  |  |  |  |

#### Parallel Poll Register

The Parallel Poll Register defines the parallel poll response of the COM 7210.

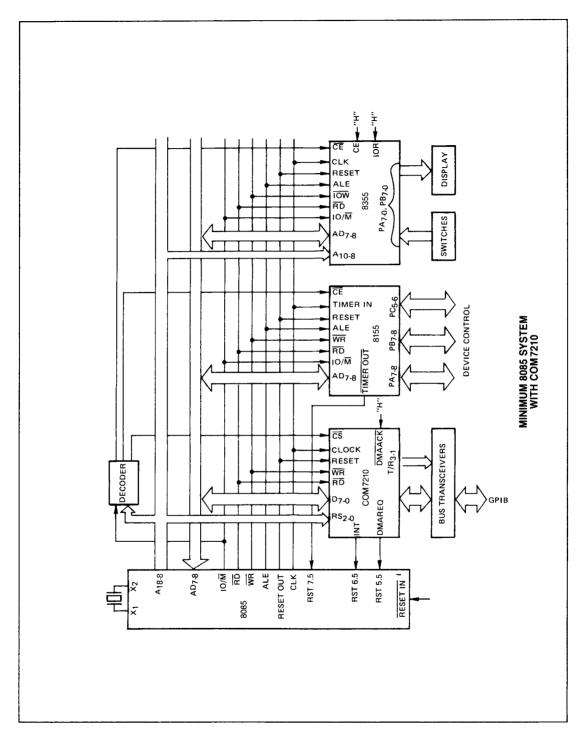

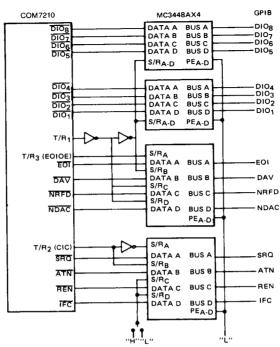

Note: In this example, high-speed data transfer cannot be made since the bus transceiver is of the open collector type (Set  $B_z\,=\,0$ ).

Note: In the case of low-speed data transfer ( $B_{\rm g}=0$ ), the T/R<sub>3</sub> pin can be used as a TRIG output. The PE input of SN75160 should be cleared to "0."

MINIMUM 8085 SYSTEM WITH COM7210 (CONT.)

### **ELECTRICAL CHARACTERISTICS**

#### MAXIMUM GUARANTEED RATINGS ( $T_a = 25^{\circ}C$ )

| PARAMETER             | SYMBOL           | RATINGS       | UNIT |

|-----------------------|------------------|---------------|------|

| Supply Voltage        | V <sub>cc</sub>  | - 0.5 ∼ + 7.0 | V    |

| Input Voltage         | V,               | −0.5 ~ + 7.0  | V    |

| Output Voltage        | V <sub>o</sub>   | − 0.5 ~ + 7.0 | V    |

| Operating Temperature | T <sub>opt</sub> | 0 ~ +70       | °C   |

| Storage Temperature   | T <sub>stq</sub> | − 65 ~ + 125  | °C   |

# DC CHARACTERISTICS ( $T_a = 0 \text{ to } +70^{\circ}\text{C}, V_{\text{CC}} = 5\text{V} \pm 10\%$ )

|                                           |                   |                | LIMITS |                       | UNIT |                                                        |  |

|-------------------------------------------|-------------------|----------------|--------|-----------------------|------|--------------------------------------------------------|--|

| PARAMETER                                 | SYMBOL            | MIN            | TYP    | MAX                   |      | TEST CONDITIONS                                        |  |

| Input Low Voltage                         | V <sub>IL</sub>   | - 0.5          |        | + 0.8                 | V    |                                                        |  |

| Input High Voltage                        | V <sub>iH</sub>   | + 2.0          |        | V <sub>cc</sub> + 0.5 | ٧    |                                                        |  |

| Low Level<br>Output Voltage               | V <sub>OL</sub>   |                |        | + 0.45                | V    | I <sub>ot</sub> = 2 mA<br>(4 mA: T/R1 Pin)             |  |

| High Level<br>Output Voltage              | V <sub>OH</sub> , | + 2.4          |        |                       | V    | I <sub>OH</sub> = −400 μA<br>(Except INT)              |  |

| High Level<br>Output Voltage<br>(INT Pin) | V <sub>OH2</sub>  | + 2.4<br>+ 3.5 |        |                       | ٧    | $I_{OH} = -400 \mu\text{A}$ $I_{OH} = -50 \mu\text{A}$ |  |

| Input Leakage<br>Current                  | I <sub>IL</sub>   | - 10           |        | + 10                  | μΑ   | $V_{\text{in}} = 0V \sim V_{\text{CC}}$                |  |

| Output Leakage<br>Current                 | loL               | - 10           |        | + 10                  | μА   | $V_{\text{OUT}} = 0.45 \text{V} \sim V_{\text{CC}}$    |  |

| Supply Current                            | I <sub>cc</sub>   |                |        | + 180                 | mA   |                                                        |  |

# $\textbf{CAPACITANCE} \ (T_a = 25^{\circ}C, \ V_{\text{CC}} = GND = 0V)$

|                    |                  |     | LIMITS |     | 1    |                                        |

|--------------------|------------------|-----|--------|-----|------|----------------------------------------|

| PARAMETER          | SYMBOL           | MIN | TYP    | MAX | UNIT | TEST CONDITIONS                        |

| Input Capacitance  | C <sub>IN</sub>  |     |        | 10  | ρF   | f = 1 MHz                              |

| Output Capacitance | Соит             |     |        | 15  | pF   | All Pins Except Pin Under Test Tied to |

| I/O Capacitance    | C <sub>i o</sub> |     |        | 20  | pF   | AC Ground                              |

AC CHARACTERISTICS,  $(T_a = 0 \text{ to } 70^{\circ}\text{C}, V_{cc} = 5\text{V} \pm 10\%)$

| AC CHARACTERISTICS, (1a o to 75 |                    | LIM | ITS                        | UNIT |                                                                                                                               |  |

|---------------------------------|--------------------|-----|----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------|--|

| PARAMETER                       | SYMBOL             | MIN | MAX                        |      | CONDITIONS                                                                                                                    |  |

| EOI 1 → DIO                     | t <sub>EOD1</sub>  |     | 250                        | ns   | PPSS → PPAS, ATN = True                                                                                                       |  |

| EOL → T/R1 *                    | t <sub>EOT11</sub> |     | 155                        | ns   | PPSS → PPAS, ATN = True                                                                                                       |  |

| EOL → T/RII                     | t <sub>EOT12</sub> |     | 200                        | ns   | PPAS → PPSS, ATN = False                                                                                                      |  |

| ATN ⊥ → NDAC ↓                  | t <sub>ATND</sub>  |     | 155                        | ns   | AIDS → ANRS, LIDS                                                                                                             |  |

| ATN. → T/B1 L                   | t <sub>ATT1</sub>  |     | 155                        | ns   | TACS + SPAS → TADS, CIDS                                                                                                      |  |

| ATN : → T/R2 ↓                  | t <sub>ATT2</sub>  |     | 200                        | ns   | TACS + SPAS → TADS, CIDS                                                                                                      |  |

| DAV → DMAREQ                    | t <sub>pvBQ</sub>  |     | 600                        | ns   | ACRS → ACDS, LACS                                                                                                             |  |

| DAV I → NFRD I                  | t <sub>ovnB1</sub> |     | 350                        | ns   | ACRS → ACDS                                                                                                                   |  |

| DAV ↓ → NDAC                    | t <sub>DVND1</sub> |     | 650                        | ns   | ACRS → ACDS → AWNS                                                                                                            |  |

| DAV: → NDAC.                    | t <sub>DVND2</sub> |     | 350                        | ns   | AWNS → ANRS                                                                                                                   |  |

| DAV ↑ → DRFD ↑                  | t <sub>DVNR2</sub> |     | 350                        | ns   | AWNS → ANRS → ACRS                                                                                                            |  |

| RD L → NRFD .                   | t <sub>ene</sub>   |     | 500                        | ns   | ANRS → ACRS<br>LACS, DI reg. selected                                                                                         |  |

| NDAC ' DMAREQ '                 | t <sub>NDRQ</sub>  |     | 400                        | ns   | STRS → SWNS → SGNS,<br>TACS                                                                                                   |  |

| NDAC · → DAV ·                  | t <sub>NDDV</sub>  |     | 350                        | ns   | STRS → SWNS → SGNS                                                                                                            |  |

| WR · → DIO                      | t <sub>woi</sub>   |     | 250                        | ns   | SGNS → SDYS, BO<br>reg. selected                                                                                              |  |

| NRFD · → DAV ₁                  | t <sub>NRDV</sub>  |     | 350                        | ns   | SDYS → STRS, T, = True                                                                                                        |  |

| WR · → DAV :                    | t <sub>wov</sub>   |     | 830<br>+ t <sub>sync</sub> | ns   | SGNS $\rightarrow$ SDYS $\rightarrow$ STRS<br>BO reg. selected, RFD = True<br>$N_F = fc = 8 \text{ MHz}$ ,<br>T, (High Speed) |  |

| TRIG<br>Pulse Width             | t <sub>raig</sub>  | 50  |                            | ns   |                                                                                                                               |  |

|                                 |                    | 85  |                            | ns   | RS0 ~ RS2                                                                                                                     |  |

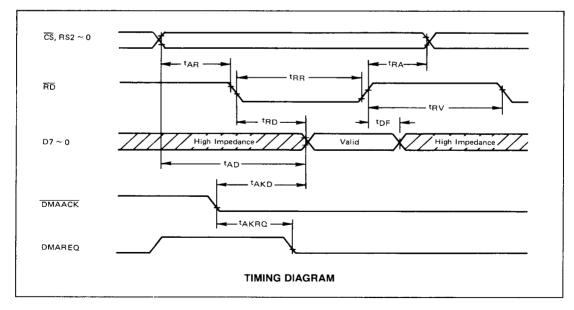

| Address Setup to RD             | t <sub>AR</sub>    | 0   |                            | ns   | CS                                                                                                                            |  |

| Address Hold from RD            | t <sub>RA</sub>    | 0   |                            | ns   |                                                                                                                               |  |

| RD Pulse Width                  | t <sub>BB</sub>    | 170 |                            | ns   |                                                                                                                               |  |

| Data Delay from Address         | t <sub>AD</sub>    |     | 250                        | ns   |                                                                                                                               |  |

| Data Delay from RD .            | t <sub>BD</sub>    |     | 150                        | ns   |                                                                                                                               |  |

| Output Float Delay from RD      | t <sub>of</sub>    | 0   | 80                         | ns   |                                                                                                                               |  |

| RD Recovery Time                | t <sub>RV</sub>    | 250 |                            | ns   |                                                                                                                               |  |

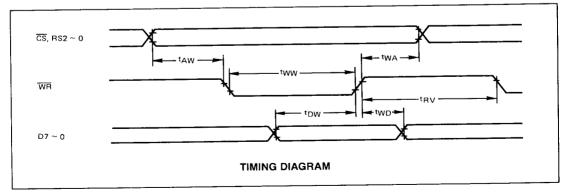

| Address Setup to WR             | t <sub>avv</sub>   | 0_  |                            | ns   |                                                                                                                               |  |

| Address Hold from WR            | t <sub>wa</sub>    | 0   |                            | ns   |                                                                                                                               |  |

| WR Pulse Width                  | t <sub>ww</sub>    | 170 |                            | ns   |                                                                                                                               |  |

| Data Setup to WR                | t <sub>ow</sub>    | 150 |                            | ns   |                                                                                                                               |  |

| Data Hold from WR               | t <sub>wD</sub>    | 0   |                            | ns   |                                                                                                                               |  |

| WR Recovery Time                | t <sub>RV</sub>    | 250 |                            | ns   |                                                                                                                               |  |

| DMAREQ   Delay from DMAACK      | t <sub>AKRQ</sub>  |     | 130                        | ns   |                                                                                                                               |  |

| Data Delay from DMAACK          | t <sub>AKD</sub>   |     | 200                        | ns_  |                                                                                                                               |  |

Circuit diagrams utilizing SMC products are included as a means of illustrating typical semiconductor applications; consequently complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of SMC or others. SMC reserves the right to make changes at any time in order to improve design and supply the best product possible.