# H3300

### 32 x 8 CMOS EEPROM

## SEMICONDUCTOR DIVISION

Industrial Electronics Group

#### DESCRIPTION

Hughes H3300 is a CMOS Electrically Erasable Programmable ROM (EEPROM), organized as 32 x 8. Read and Write operations are performed with a single 5V power supply using simple TTL level control signals.

Writing data into nonvolatile storage is performed in a manner similar to the write control of a static RAM. A short logic low pulse to the  $\overline{\text{WE}}$  pin (Write Enable) initiates the Byte Write operation which is completed with on-chip timing (a separate Erase operation is not required). Addresses and data are internally latched to free the system bus for other tasks during the Write period.

A Read operation is performed by presenting the byte address and enabling the chip with  $\overline{CE}$  (Chip Enable) low. The device uses a two-line control architecture,  $\overline{CE}$  and  $\overline{OE}$  (Output Enable), to eliminate bus contention in a system environment.

Hughes H3300 is available in an 18 lead hermetic dual-in-line ceramic package (D suffix) and plastic package (P suffix). Devices in chip form (H suffix) are available upon request. Commercial (HC3300), Industrial (HI3300), and Military (HB3300) versions are available.

### **FEATURES**

- Byte wide organization 32 x 8 bit

- · Single 5V power supply Read and Write

- · Very low power dissipation CMOS

- Byte programmable with No Erase required

- · On chip timing for Byte Write

- · On chip Address & Data latches

- Simple and efficient 3-line control (CE, OE, WE)

- 10 Year Data Retention<sup>3</sup>

- 10,000 Byte Write Cycles (Endurance)2

### PIN CONFIGURATION

### **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

DC Supply Voltage Range . . . . - 0.3 to +6 V (All voltages referenced to GND pin)

Input Voltage Range . . . . . - 0.3 to VDD +0.3 V

Storage Temperature Range . . . - 65 °C to +150 °C

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

|                   |                 | Read Mode Write Mode |                    |  |  |  |  |  |

|-------------------|-----------------|----------------------|--------------------|--|--|--|--|--|

| Supply Voltage    |                 | 5 V ± 5%             | 5V ± 5%            |  |  |  |  |  |

|                   | Plastic Package | - 40 °C to +85 °C    | - 40 °C to + 85 °C |  |  |  |  |  |

| Temperature Range | Ceramic Package | - 55 °C to + 125 °C  | - 55 °C to +125 °C |  |  |  |  |  |

### DC OPERATING CHARACTERISTICS

Read: V<sub>DD</sub> = 5V ±5% Unless Otherwise Specified

| Symbol          | - Company                       | + 2510 |       |      | -40°C to +85°G |      | -55 °C 10'+ 125 °C |      | a di di | Took 1997                                |

|-----------------|---------------------------------|--------|-------|------|----------------|------|--------------------|------|---------|------------------------------------------|

|                 |                                 | Min.   | Typ.  | Max. | Min.           | Max. | Min.               | Max. | Units   | Test<br>Constitions                      |

| loos            | V <sub>DD</sub> Standby Current | _      | 25    | 100  | _              | 200  |                    | 200  | μΑ      | CE = WE = 5V, OE =<br>0 All I/O's = open |

| IDDA            | V <sub>DD</sub> Active Current' | -      | 25    | 100  | _              | 200  | _                  | 200  | μА      | CE = OE = 0, WE =<br>5V All I/O's = open |

| VOL             | Output Low Voltage              | T-     | 0.25  | 0.45 |                | 0.45 | _                  | 0.45 | v       | IOL = 2.1mA                              |

| VOH             | Output High Voltage             | 3.0    | 4.5   | -    | 3.0            | _    | 3.0                | _    | v       | IOH = -400 μA                            |

| V <sub>IL</sub> | Input Low Voltage               | -      | -     | 0.8  | _              | 0.8  | _                  | 0.8  | ٧       | _                                        |

| V <sub>IH</sub> | Input High Voltage              | 3.2    | -     | Ī —  | 3.2            | _    | 3.2                |      | V       |                                          |

| ILI             | Input Leakage Current           | -      | ± 0.1 | ± 10 | _              | ± 10 |                    | ± 10 | μА      | VIN = 0 or 5V                            |

| ILO             | Output Leakage Current          | 1 -    | ±0.3  | ± 10 | _              | ± 10 | _                  | ± 10 | μА      | VOUT = 0 or 5V                           |

#### Notes:

- (1) This parameter is sampled only and is not 100% tested.

- (2) Endurance is the number of possible Write cycles per byte.

- (3) Retention is the amount by time data is retained in memory without power applied.

Read:  $V_{DD} = 5V \pm 5\%$  Unless Otherwise Specified

|                  | Puraneous                                      | + <b>3</b> °C |      |      | 40°C IA + 86°C |     | -461G/o+1261C |      |       |                                                            |  |

|------------------|------------------------------------------------|---------------|------|------|----------------|-----|---------------|------|-------|------------------------------------------------------------|--|

| Symbol           |                                                | Mirc          | 1792 | Nas. | Mitte          | -   | -Keine        | Max. | Unite | Cardition                                                  |  |

| <sup>t</sup> CEH | CE High Time                                   | 350           | 200  | _    | 450            | _   | 600           | _    | ns    | WE =V <sub>IH</sub> ,<br>CElow time= <sup>†</sup> ACE(Max) |  |

| <sup>t</sup> ACE | Chip Enable Access Time                        | _             | 400  | 500  | _              | 650 | _             | 700  | ns    | WE = VIH                                                   |  |

| <sup>t</sup> OE  | Output Enable Access Time                      | _             | 225  | 275  | _              | 350 | -             | 375  | ns    | WE = VIH                                                   |  |

| <sup>t</sup> ASU | Address Set Up Time                            | 100           | 25   | _    | 165            | _   | 250           | _    | ns    | WE =VIH                                                    |  |

| tAH              | Address Hold Time                              | 50            | 25   | _    | 50             | _   | 50            | _    | ns    | WE =VIH                                                    |  |

| tон              | Output Hold from<br>OE or CE High <sup>1</sup> | 0             | _    | _    | 0              | _   | 0             | _    | ns    | WE = VIH                                                   |  |

| <sup>t</sup> DF  | Output Float from<br>OE or CE High             | _             | _    | 400  | _              | 475 | _             | 525  | ns    | WE = VIH                                                   |  |

| DDR              | Dynamic Read Current                           | _             | 0.3  | .5   | _              | .5  | _             | .5   | mA    | f = 100 KHz                                                |  |

Write: V<sub>DD</sub> = 5V ± 5% Unless Otherwise Specified

|                  |                       |            | 25°C  |      | -40703 | 1 + 15 °C, | 45:C1 | 14 125 10 | Ast.   |                        |

|------------------|-----------------------|------------|-------|------|--------|------------|-------|-----------|--------|------------------------|

| Sympa            | Parameter 1           | <b>New</b> | Typ.  | Max. | *****  | Hec        |       | Mex       | brit e | Conditions             |

| <sup>t</sup> CES | CE Set Up Time        | 0          | _     | _    | 0      | _          | 0     | -         | ns     | OE = VIH               |

| <sup>t</sup> CEH | CE Hold Time          | 0          | -     | _    | 0      |            | 0     |           | ns     | OE = VIH               |

| twp              | Write Pulse Width     | 500        | 350   | _    | 650    | _          | 700   | _         | ns     | OE = VIH               |

| tASP             | Address Set Up Time   | 100        | 25    | _    | 165    | _          | 250   | _         | ns     | ÕE = VIH               |

| <sup>t</sup> AHP | Address Hold Time     | 50         | 25    | -    | 50     | _          | 50    | _         | ns     | OE = VIH               |

| tDS              | Data Set Up Time      | 0          | - 200 | _    | 0      | _          | 0     | _         | ns     | OE = VIH               |

| <sup>t</sup> DH  | Data Hold Time        | 325        | 240   | _    | 400    | _          | 450   |           | ns     | OE = VIH               |

| tWES             | WE Set Up Time        | 0          | _     | _    | 0      | _          | 0     |           | ns     | OE = VIH               |

| tWEH             | WE Hold Time          | 0          | _     | _    | 0      | _          | 0     | _         | ns     | OE = VIH               |

| tρ               | Program Cycle Time    | _          | 5     | 10   | _      | 10         | _     | 10        | ms     | OE = VIH, CE = VIL     |

| DDW              | Dynamic Write Current | _          | .3    | .8   | _      | 1.0        | _     | 1.0       | mA     | f =100 Hz, VDD = 5.25V |

**AC TEST CONDITIONS**

Output Load:  $C_L = 50 \text{ pF}$  Timing Measurement Reference Level: Input = 0utput = 50% VDD Input Levels:  $V_H = 3.2 \text{ V}$ ,  $V_L = 0.4 \text{ V}$  Input Rise and Fall Time:  $t_r = t_r = 10 \text{ ns}$

### **OPERATING MODES**

Logic 1 = High, Logic 0 = Low, X = Do Not Care

| MODE       | CE | ŎE . | WE | I/O BUS     |

|------------|----|------|----|-------------|

| Standby    | 1  | х    | ×  | Floating    |

| Read       | 0  | 1    | 1  | Floating    |

| Read       | 0  | 0    | 1  | Data Output |

| Write      | 0  | 1    | 0  | Data Input  |

| Prohibited | 0  | 0    | 0  | Active      |

STANDBY MODE: With  $\overline{\text{CE}}$  high the circuit is inactive, independent of the state of any other input.

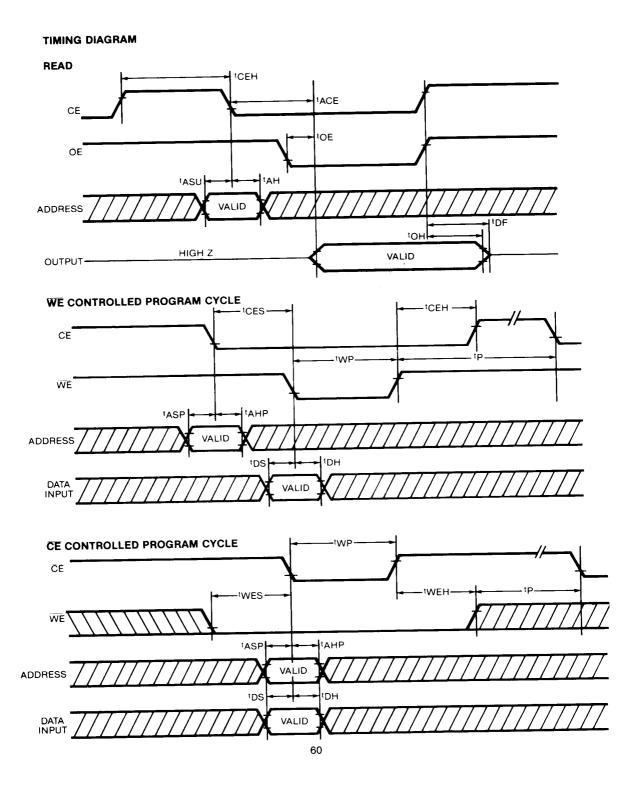

**READ MODE:**

The falling edge of CE latches the input address and initiates a Read cycle. When CE is low, a low input to OE turns on the three-state output bus drivers.

WRITE MODE:

Two Write control modes are made possible:

(1) With a WE controlled mode, the cycle is initiated with CE going low which latches the input address. When WE is taken low the input data is latched and the self timed program cycle begins when WE returns high.

(2) With a CE controlled mode, the cycle is initiated with WE going low. Both input address and data are latched when CE goes low and the self timed program cycle begins when WE returns high.

**PROHIBITED**

MODE:

A Write Cycle will occur in this mode and the three-state output drives will be turned on, creating a bus contention problem for normal writes.

#### PIN DESCRIPTION

A 0 - A 4: Address inputs which select one of 32 bytes of memory for either Read or Write.

I/O 0 - I/O 7: Bidirectional three-state data lines that are data outputs during Read and data inputs dur-

ing Writes.

**GND:** Negative supply terminal and V = 0 reference

**VDD:** Positive supply terminal

CE: Chip Enable. This input causes the circuit to latch the input address and initiate a Read

cycle when taken low. Read data remains valid while  $\overline{\text{CE}}$  is held low. It also enables the

WE input when low.

Output Enable. This input turns on the three-state output bus drivers when CE is low.

WE: Write Enable. This input latches the data input when taken low if CE is low. A self timed

Write cycle begins when WE is returned high.