## INTRODUCTION

The KS0104 is a LCD driver LSI which is fabricated by low power CMOS high voltage process technology. This device consists of 80 bit bidirectional shift register, 80 bit data latch and 80 bit driver

# FUNCTION

•Dot matrix LCD segment driver with 80 channel output

- Input/Output signal

- Input : 4 bit parallel display data, control pulse from controller and bias voltage (V<sub>1</sub>,V<sub>3</sub>, V<sub>4</sub>, V<sub>EE</sub>)

- Output ; 80 channel waveform for LCD driving.

- Power down function to make power consumption low.

# FEATURES

- Power supply voltage : + 5V  $\pm$  10%

- \* Supply voltage for display : 8 ~ 28V (  $V_{\text{DD}}$   $V_{\text{EE}}$  )

- Parallel data processing (4 bit )

- Applicable LCD duty : 1/64 ~ 1/256

- Interface

| Driver               |                |

|----------------------|----------------|

| COMMON               | SEG ( cascade) |

| KS0083/84/86, KS0103 | Other KS0104/B |

- · High voltage CMOS process

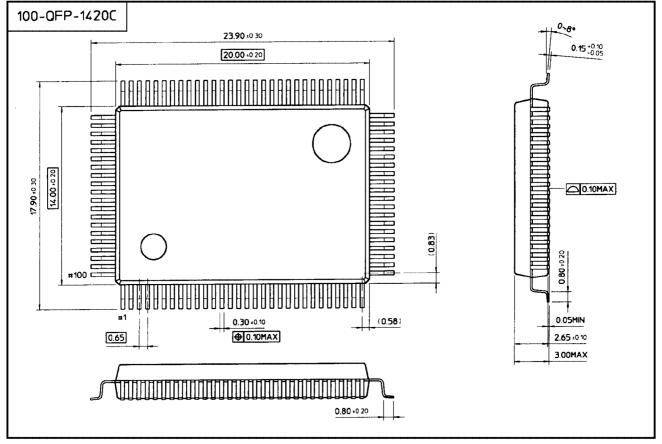

- 100 QFP and bare chip available.

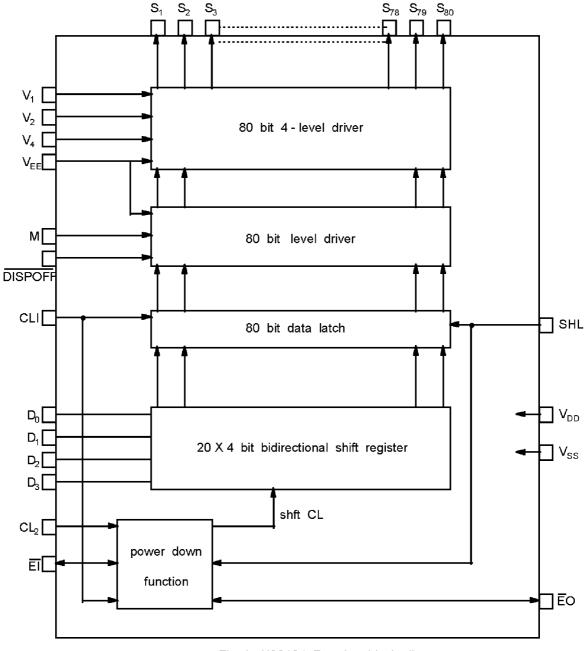

# **BLOCK DIAGRAM**

Fig 1. KS0104 Function block diagram

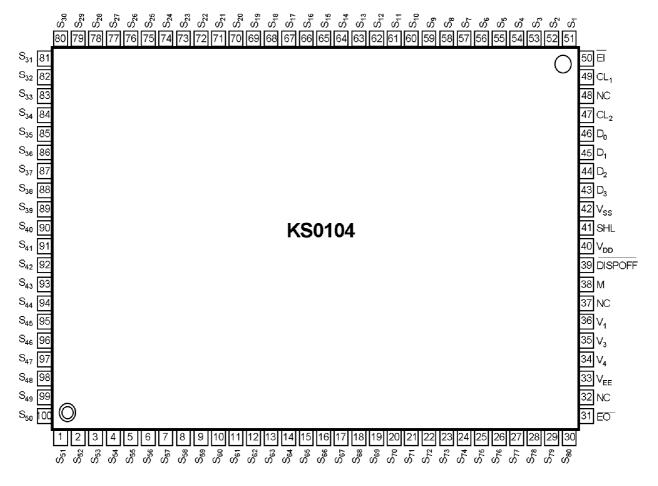

### PIN CONFIGURATION

Fig. 2. 100 QFP Top View

# MAXIMUM ABSOLUTE LIMIT

| Characteristic        | Symbol           | Value                     | Unit |

|-----------------------|------------------|---------------------------|------|

| Operating Voltage     | V <sub>DD</sub>  | -0.3~6.0                  | V    |

| Driver Supply Voltage | VLCD             | 0~30                      | V    |

| Input Voltage         | V <sub>IN</sub>  | -0.3~V <sub>DD</sub> +0.3 | V    |

| Operating Temperature | T <sub>OPR</sub> | -30~+85                   | C    |

| Storage Temperature   | T <sub>STG</sub> | -55~+150                  | Ĉ    |

\* Voltage greater than above may result in damage to the circuit.

#### **ELECTERICAL CHARACTERISTICS**

DC Characteristics (V<sub>DD</sub>=5V $\pm$ 10%, V<sub>SS</sub>=0V, Ta=-30 ~ +85  $^\circ$ C, C<sub>L</sub>=15pF)

| Characteristics       | Symbol              |                                                                | Condition                                      |                      |     | Мах         | Unit |

|-----------------------|---------------------|----------------------------------------------------------------|------------------------------------------------|----------------------|-----|-------------|------|

| Operating Voltage     | V <sub>DD</sub>     |                                                                | -                                              |                      |     | 5.5         |      |

| Driver Supply Voltage | $V_{DD}$ - $V_{EE}$ |                                                                | -                                              | 8                    | -   | 28          | v    |

| Input Voltage (*1)    | VIH                 |                                                                | -                                              | $0.8V_{DD}$          | -   | -           |      |

|                       | VIL                 |                                                                | -                                              |                      |     | $0.2V_{DD}$ |      |

| Input Current (*1)    | I <sub>IH</sub>     | VII                                                            | -                                              | -                    | 1   | μA          |      |

|                       | IIL                 | V                                                              | <sub>H</sub> =0V, V <sub>DD</sub> =5.5V        | -                    | -   | -1          |      |

| Output Voltage (*2)   | V <sub>OH</sub>     | I <sub>0</sub> =-                                              | 0.2mA, V <sub>DD</sub> =4.5V                   | V <sub>DD</sub> -0.4 | -   | -           | V    |

|                       | V <sub>OL</sub>     | l <sub>o</sub> =                                               | -                                              | -                    | 0.4 |             |      |

| On Resistance(*3)     | R <sub>ON</sub>     | $V_{DD}$ - $V_{EE}$ =23V, $V_{D}$                              | <sub>D</sub> =4.5V (*4)   Vn-Vo   =0.25V       | -                    | 2   | 4           | KΩ   |

| Supply Current (*5)   | I <sub>SBY</sub>    | CL2=1MHz                                                       | CL2=1MHz Display data is not processing        |                      | -   | 200         | μA   |

|                       | I <sub>DD</sub>     | V <sub>DD</sub> =5.5V<br>V <sub>DD</sub> -V <sub>FF</sub> =26V | Display data is processing                     | -                    | -   | 3           | шA   |

|                       | ١v                  | VDD-VEE-20V                                                    | Current on $V_1$ , $V_3$ , $V_4$ $V_{EE}$ pins | -                    | -   | ±100        | μA   |

| Input Capacitance     | Ci                  |                                                                | f=1MHz                                         |                      |     | -           | pF   |

\*1; Applicable pin; CL<sub>1</sub>, CL<sub>2</sub>, EI, EO, D<sub>0</sub>-D<sub>3</sub>, SHL, DISPOFF, M

\*2; Applicable pin; EI, EO

\*3; Applicable pin; S1-S80

\*4; Vn=VDD-VEE, V3=13/15 (VDD-VEE), V4=2/15 (VDD-VEE), VDD=V1

\*5; Display data 1010-M=40Hz.

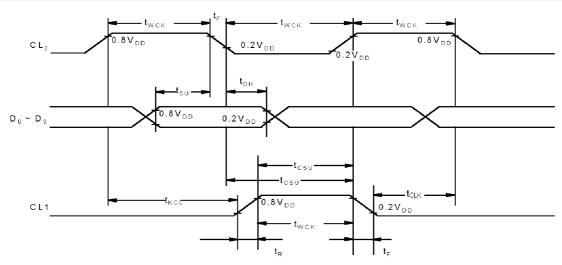

| Characteristic              | Symbol                         | Condition        | Min | Тур | Мах | Unit |

|-----------------------------|--------------------------------|------------------|-----|-----|-----|------|

| Clock Frequency             | f <sub>CL</sub>                | Dut <b>y=50%</b> | 3.4 | -   | -   | MHz  |

| Clock Pulse Width           | t <sub>vv</sub>                | -                | 100 | -   | -   |      |

| Clock Rise/Fall Time        | t <sub>R</sub> ,t <sub>F</sub> | -                | -   | -   | 50  |      |

| Data Set-up Time            | ts∪                            | -                | 50  | -   | -   |      |

| Data Hold Time              | t <sub>DH</sub>                | -                | 80  | -   | -   |      |

| Clock-CL <sub>1</sub> Time  | t <sub>KCL</sub>               | -                | 200 | -   | -   | ns   |

| CL <sub>1</sub> Set-up Time | t <sub>csu</sub>               | -                | 90  | -   | -   |      |

| CL <sub>1</sub> -Clock Time | t <sub>cLK</sub>               | -                | 200 | -   | -   |      |

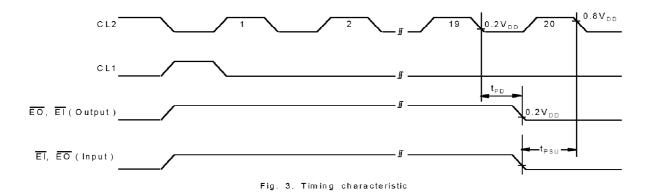

| Propagation Delay Time      | t <sub>PD</sub>                | EO Output        | -   | -   | 224 |      |

|                             |                                | El Output        |     |     | 224 |      |

| EO, El Set-up Time          | t <sub>PSU</sub>               | EO Input         | 70  | -   | -   | 1    |

|                             |                                | El Input         | 70  |     |     |      |

# AC Characteristics (V\_DD=+5V $\pm$ 10%, V\_SS=0V, T\_a=-30 ~ +85 $^\circ \!\! C$ , C\_L=15pF)

### **PIN DESCRIPTION**

| PIN<br>(No)                     | INPUT<br>OUTPUT | N/        | AME          |       | DES                                                                                                            | SCRIPTION                                                              | INTERFACE    |  |  |  |

|---------------------------------|-----------------|-----------|--------------|-------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------|--|--|--|

| V <sub>DD</sub> (40)            | 001101          | Operatir  | ng Voltage   | Fo    | r logical circuit (+5V±10%)                                                                                    | )                                                                      | Power        |  |  |  |

| V <sub>SS</sub> (42)            | Power           |           |              |       | (GND)                                                                                                          |                                                                        | Supply       |  |  |  |

| V <sub>EE</sub> (33)            |                 | Negativ   | e Supply     | Fo    | r LCD drive circuit                                                                                            |                                                                        |              |  |  |  |

|                                 |                 | Vo        | ltage        |       |                                                                                                                |                                                                        |              |  |  |  |

| V <sub>1</sub> , V <sub>3</sub> | Input           | LCD dri   | ver output   | Bia   | is supply voltage terminals                                                                                    | to drive the LCD.                                                      | Power        |  |  |  |

| V4                              |                 | volta     | ge level     |       | is voltage divded by the res                                                                                   | -                                                                      |              |  |  |  |

| (34-36)                         | <u> </u>        |           |              | _     | ed as supply voltage source                                                                                    | · · · · · · · · · · · · · · · · · · ·                                  |              |  |  |  |

| S <sub>1</sub> ~S <sub>80</sub> | Output          | LCD dri   | ver output   |       | splay data output pin which<br>ch contents.                                                                    | corresponds to the respective                                          | LCD          |  |  |  |

| (1-30,<br>51-100)               |                 |           |              |       |                                                                                                                |                                                                        |              |  |  |  |

| 31-100)                         |                 |           |              |       | e of V <sub>1</sub> , V <sub>3</sub> , V <sub>4</sub> and V <sub>EE</sub> is se<br>tage source according to th |                                                                        |              |  |  |  |

|                                 |                 |           |              |       | el and M signal (refer to no                                                                                   |                                                                        |              |  |  |  |

| CL <sub>2</sub> (47)            | Input           | Data s    | hift clock   | _     |                                                                                                                | parallel shift register. The data is                                   | Controller   |  |  |  |

|                                 |                 |           |              |       | fted to 80 bit shift register a                                                                                | at the falling edge of the clock pulse.                                |              |  |  |  |

|                                 |                 |           |              |       | e clock pulse, which was in                                                                                    |                                                                        |              |  |  |  |

|                                 |                 |           |              | -     | not active condition, is inval<br>ernate signal input pin for L                                                |                                                                        |              |  |  |  |

| M(38)                           | Input           | Alterna   | Controller   |       |                                                                                                                |                                                                        |              |  |  |  |

|                                 |                 |           | D driver     | ····· |                                                                                                                |                                                                        |              |  |  |  |

|                                 |                 |           | itput        |       | The signal for latching the shift register contents is input to this                                           |                                                                        |              |  |  |  |

| CL <sub>1</sub> (49)            | Input           |           | tch clock    |       | Controller                                                                                                     |                                                                        |              |  |  |  |

|                                 |                 |           |              |       | minal.<br>1 pulse "H" level initializes                                                                        |                                                                        |              |  |  |  |

| DISPOF                          | Input           | Output le | evel control | _     | Control input pin for display data output level ( $S_1 \sim S_{80}$ ). $V_1$                                   |                                                                        |              |  |  |  |

| (39)                            |                 |           |              |       |                                                                                                                | minal during "L" level input.                                          |              |  |  |  |

|                                 |                 |           |              |       | LCD becomes non-selected by $V_1$ level output from every                                                      |                                                                        |              |  |  |  |

|                                 |                 |           |              | ഡ     | put of segment drivers and                                                                                     | every output of common drivers.                                        |              |  |  |  |

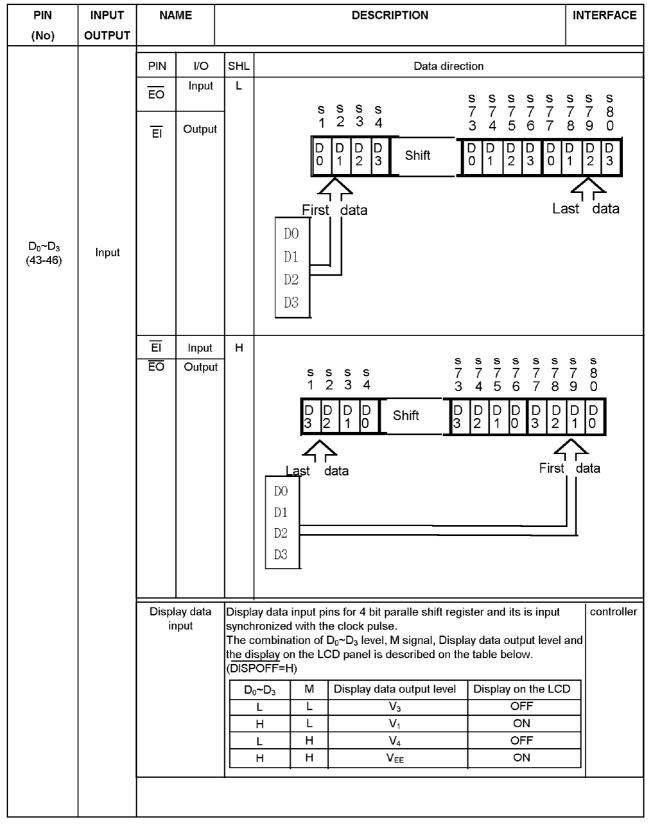

| SHL(41)                         | Input           | C         | )ata         |       |                                                                                                                | her input terminal or output                                           |              |  |  |  |

| EO,EI                           | Input           | inte      | erface       |       | minal according to the cond                                                                                    |                                                                        |              |  |  |  |

| (31,50)                         | Output          |           |              |       | e shif <u>ting</u> direction of each                                                                           |                                                                        |              |  |  |  |

|                                 |                 |           |              |       | and EI, and the condition (                                                                                    |                                                                        |              |  |  |  |

|                                 |                 |           |              | Iner  | ow. (refer to note 3)                                                                                          |                                                                        |              |  |  |  |

|                                 |                 | Pin       | I/O          | SHL   | Display data<br>shift direction                                                                                | Description                                                            |              |  |  |  |

|                                 |                 |           |              |       | shint direction                                                                                                |                                                                        |              |  |  |  |

|                                 |                 | ĒŌ        | Input        |       | $D_0; S_1 \rightarrow S_5 \rightarrow S_{77}$<br>$D_1; S_2 \rightarrow S_6 \rightarrow S_{78}$                 | Input terminal to ENABLE F/F of KS0                                    | 0104         |  |  |  |

|                                 |                 | EL        | Output       | L     | $D_2; S_3 \rightarrow S_7 \rightarrow S_{79}$                                                                  | Output terminal of ENABLE F/F. El is                                   |              |  |  |  |

|                                 |                 |           |              |       | $D_3; S_4 \rightarrow S_8 \rightarrow S_{80}$                                                                  | to next KS0104's EO when the KS01                                      |              |  |  |  |

|                                 |                 |           |              |       |                                                                                                                | connected in series (cascade conne                                     |              |  |  |  |

|                                 | ET Input        |           |              |       | D <sub>0</sub> ; S <sub>80</sub> →S <sub>76</sub> →S <sub>4</sub>                                              | Input terminal to ENABLE F/F of KS0                                    | 0104         |  |  |  |

|                                 |                 | EO        | Output       | Н     | $D_1; S_{79} \rightarrow S_{75} \rightarrow S_3$                                                               | Output terminal of ENABLE F/F.                                         | <del>.</del> |  |  |  |

|                                 |                 |           |              |       | $D_2; S_{78} \rightarrow S_{74} \rightarrow S_2$                                                               | EO is connected to next KS0104's E<br>KS0104's are connected in series | l when the   |  |  |  |

|                                 |                 |           |              |       | D <sub>3</sub> ; S <sub>77</sub> →S <sub>73</sub> →S <sub>1</sub>                                              | (cascade connection)                                                   |              |  |  |  |

|                                 |                 |           |              |       |                                                                                                                |                                                                        |              |  |  |  |

|                                 |                 |           |              |       |                                                                                                                |                                                                        |              |  |  |  |

|                                 |                 |           |              |       |                                                                                                                |                                                                        |              |  |  |  |

#### PIN DESCRIPTION (continued)

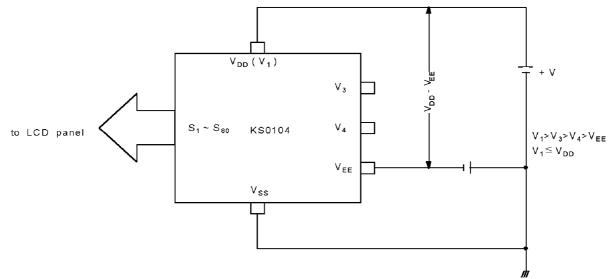

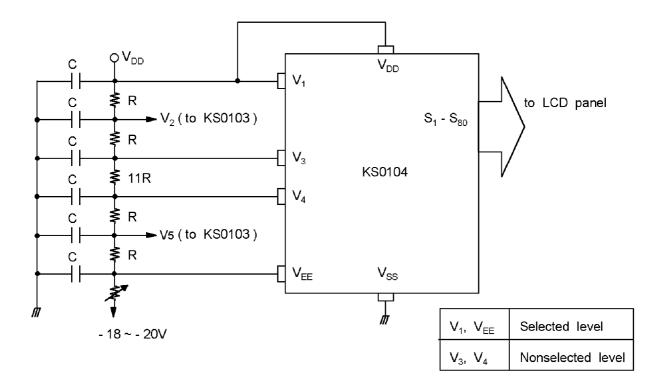

#### \*NOTE 1

The below figure shows when the bias voltage is devided by the resistor (1/15 Bias, 1/200 Duty)

\*NOTE 2

| М | Latched data | DISPOFF | Output level (S1-S80) |

|---|--------------|---------|-----------------------|

| L | L            | н       | ٧3                    |

| L | н            | н       | V1                    |

| н | L            | н       | V4                    |

| н | н            | н       | VEE                   |

| Х | Х            | L       | V1                    |

X : Don't Care

#### \*NOTE 3

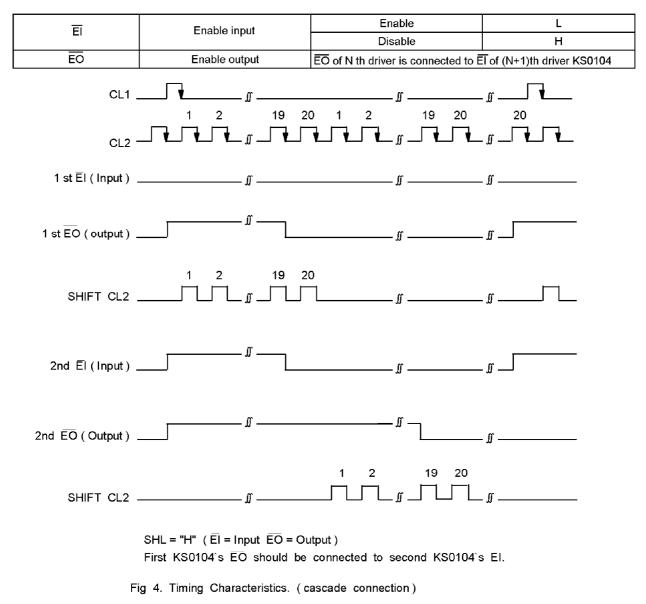

- EO and EI pins working as input terminals.

- ENABLE F/F stops Display Data in at "H" level input. ENABLE F/F starts Display data in at "L" level input.

EO and EI pins working as output terminals.

These terminals are set to the "H" level immediately after ENABLE F/F is intialized by the load pulse. Upon completion of 80-bit serial/parallel conversion using the shift clock input from the CL2 terminal, these terminals are then set to the "L" level.

The operation of ENABLE F/F is terminated and held unchanged until the next load pulse is detected. (For cascade connection, refer to the application circuit drawing.)

### POWER DOWN FUNCTION

In order to reduce the power consumption, in case of cascade connection, KS0104 has a "power down function."

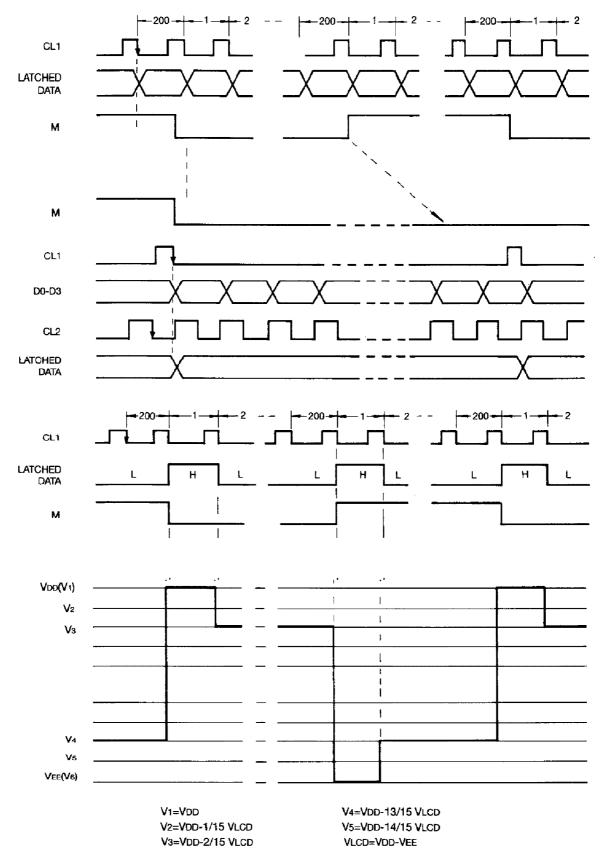

### Timing Chart - 1/200 Duty, 1/15 Bias

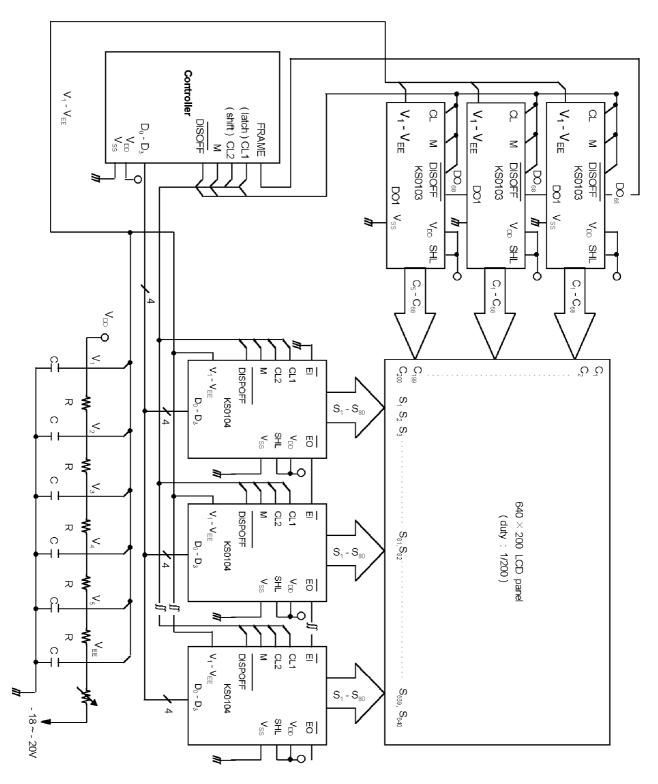

# **APPLICATION CIRCUIT**

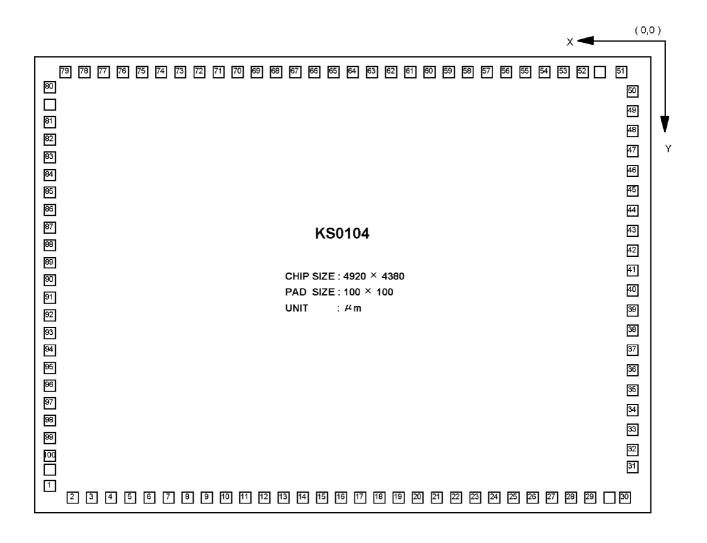

# PAD DIAGRAM

#### PAD LOCATION

| PAD<br>NUMBER | PAD  |      |        | PAD    | PAD     | COORE | DINATE | PAD    | PAD  | COORDINATE |       |

|---------------|------|------|--------|--------|---------|-------|--------|--------|------|------------|-------|

|               | NAME | х    | Y      | NUMBER | NAME    | х     | Y      | NUMBER | NAME | х          | Y     |

| *             | NC   | 4788 | 3838.5 | 34     | V4      | 130   | 3419   | 68     | S18  | 2913       | 135   |

| 1             | S51  | 4788 | 4091   | 35     | V3      | 130   | 3230.5 | 69     | S19  | 3063       | 135   |

| 2             | S52  | 4563 | 4248   | 36     | V1      | 130   | 3042   | 70     | S20  | 3213       | 135   |

| 3             | S53  | 4413 | 4248   | 37     | NC      | *     | *      | 71     | S21  | 3363       | 135   |

| 4             | S54  | 4263 | 4248   | 38     | М       | 130   | 2808   | 72     | S22  | 3513       | 135   |

| 5             | S55  | 4113 | 4248   | 39     | DISPOFF | 130   | 2573   | 73     | S23  | 3663       | 135   |

| 6             | S56  | 3963 | 4248   | 40     | VDD     | 130   | 2383   | 74     | S24  | 3813       | 135   |

| 7             | S57  | 3813 | 4248   | 41     | SHL     | 130   | 2158.5 | 75     | S25  | 3963       | 135   |

| 8             | S58  | 3663 | 4248   | 42     | VSS     | 130   | 1971.5 | 76     | S26  | 4113       | 135   |

| 9             | S59  | 3513 | 4248   | 43     | D3      | 130   | 1776.5 | 77     | S27  | 4263       | 135   |

| 10            | S60  | 3363 | 4248   | 44     | D2      | 130   | 1541.5 | 78     | S28  | 4413       | 135   |

| 11            | S61  | 3213 | 4248   | 45     | D1      | 130   | 1365   | 79     | S29  | 4563       | 135   |

| 12            | S62  | 3063 | 4248   | 46     | D0      | 130   | 1130   | 80     | S30  | 4788       | 292   |

| 13            | S63  | 2913 | 4248   | 47     | CL2     | 130   | 953.5  | *      | NC   | 4788       | 544.8 |

| 14            | S64  | 2763 | 4248   | 48     | NC      | *     | *      | 81     | S31  | 4788       | 694.5 |

| 15            | S65  | 2613 | 4248   | 49     | CL1     | 130   | 718.5  | 82     | S32  | 4788       | 844.5 |

| 16            | S66  | 2463 | 4248   | 50     | ĒĪ      | 130   | 485.5  | 83     | S33  | 4788       | 994.8 |

| 17            | S67  | 2313 | 4248   | 51     | S1      | 150   | 135    | 84     | S34  | 4788       | 1144. |

| 18            | S68  | 2163 | 4248   | *      | NC      | 363   | 135    | 85     | S35  | 4788       | 1311. |

| 19            | S69  | 2013 | 4248   | 52     | S2      | 513   | 135    | 86     | S36  | 4788       | 1471. |

| 20            | S70  | 1863 | 4248   | 53     | S3      | 663   | 135    | 87     | S37  | 4788       | 1631. |

| 21            | S71  | 1713 | 4248   | 54     | S4      | 813   | 135    | 88     | S38  | 4788       | 1791. |

| 22            | S72  | 1563 | 4248   | 55     | S5      | 963   | 135    | 89     | S39  | 4788       | 1951. |

| 23            | S73  | 1413 | 4248   | 56     | S6      | 1113  | 135    | 90     | S40  | 4788       | 2111. |

| 24            | S74  | 1263 | 4248   | 57     | S7      | 1263  | 135    | 91     | S41  | 4788       | 2271. |

| 25            | S75  | 1113 | 4248   | 58     | S8      | 1413  | 135    | 92     | S42  | 4788       | 2431. |

| 26            | S76  | 963  | 4248   | 59     | S9      | 1563  | 135    | 93     | S43  | 4788       | 2591. |

| 27            | S77  | 813  | 4248   | 60     | S10     | 1713  | 135    | 94     | S44  | 4788       | 2751. |

| 28            | S78  | 663  | 4248   | 61     | S11     | 1863  | 135    | 95     | S45  | 4788       | 2911. |

| 29            | S79  | 513  | 4248   | 62     | S12     | 2013  | 135    | 96     | S46  | 4788       | 3071. |

| *             | NC   | 363  | 4248   | 63     | S13     | 2163  | 135    | 97     | S47  | 4788       | 3238. |

| 30            | S80  | 253  | 4248   | 64     | S14     | 2313  | 135    | 98     | S48  | 4788       | 3388. |

| 31            | ĒŌ   | 130  | 3871   | 65     | S15     | 2463  | 135    | 99     | S49  | 4788       | 3538. |

| 32            | NC   | *    | *      | 66     | S16     | 2613  | 135    | 100    | S50  | 4788       | 3688. |

| 33            | VEE  | 130  | 3607.5 | 67     | S17     | 2763  | 135    |        |      |            |       |

Dimensions in Milimeters