# 1024 BIT (64 × 16) SERIAL NMOS EEPROM

- SINGLE SUPPLY READ/WRITE/ERASE OPERATIONS (5V ± 10%)

- TTL COMPATIBLE

- 64 × 16 READ/WRITE MEMORY

- LOW STANDBY CURRENT

- LOW COST SOLUTION FOR NON VOLATILE ERASE AND WRITE MEMORY

- **RELIABLE FLOTOX PROCESS**

- SELF-TIMED PROGRAMMING CYCLE

- DEVICE STATUS SIGNAL DURING PROGRAMMING

- POWÉR-ON/OFF DATA PROTECTION CIRCUITRY

- AUTOERASE

- BULK PROGRAMMING ENABLE OR DISABLE FOR ENHANCED DATA PROTECTION

#### DESCRIPTION

The M9346 is a 1024 bit non-volatile sequential access memory manufactured using SGS-THOMSON FLOATING GATE process. It is a peripheral memory designed for data storage and/or timing and is accessed via a simple serial interface. The device contains 1024 bits organized as 64x16. Written information is stored in a floating gate cell until updated by an erase and write cycle.

Bulk programming instructions (Chip Erase, Chip Write) can be enabled or disabled by the user for enhanced data protection. The M9346 has been designed for applications requiring up to 10<sup>4</sup> erase/write cycles per register. A power down mode allows a consumption decrease by 75%.

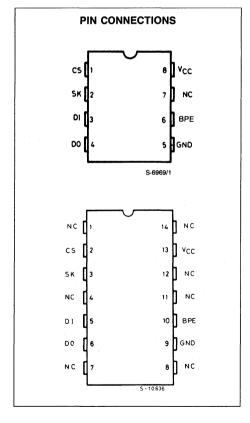

#### PIN NAMES

| ELECT  . DATA CLOCK  . DATA INPUT |

|-----------------------------------|

|                                   |

| . DATA INPUT                      |

|                                   |

| . DATA OUTPUT                     |

| RSUPPLY                           |

| 1D                                |

| PROGRAMMING ENABLE                |

| NNECT                             |

|                                   |

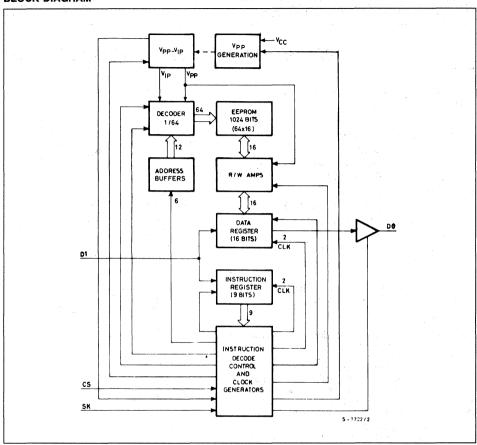

# **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                        | Values                   | Unit |  |

|------------------|--------------------------------------------------|--------------------------|------|--|

| V <sub>I</sub>   | Voltage Relative to GND                          | + 6V to -0.3             | ٧    |  |

| T <sub>amb</sub> | Ambient Operating Temperature: standard extended | 0 to + 70<br>- 40 to +85 | °C   |  |

| T <sub>stg</sub> | Ambient Storage temperature                      | -65 to + 125             | °C   |  |

Stresses in excess of those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions in excess of those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability (except for Tamb).

**ELECTRICAL CHARACTERISTICS** (0° to  $+70^{\circ}$ C, for standard Temperarure/ $-40^{\circ}$  to  $+85^{\circ}$ C for extended Temperarure,  $V_{CC} = 5V \pm 10\%$  unless otherwise specified)

| Symbol                                                    | Parameter                            | Test Conditions                                             | Min.            | Тур. | Max.                      | Unit |

|-----------------------------------------------------------|--------------------------------------|-------------------------------------------------------------|-----------------|------|---------------------------|------|

| V <sub>CC</sub>                                           | Operating Voltage                    |                                                             | 4.5             |      | 5.5                       | V    |

| l <sub>CC1</sub>                                          | Operating Current                    | V <sub>CC</sub> = 5.5V, CS = 1                              |                 | 1.5  | 12                        | mA   |

| I <sub>CC2</sub>                                          | Standby Current                      | V <sub>CC</sub> = 5.5V, CS = 0                              |                 | 1.2  | 3                         | mA   |

| Іссз                                                      | E/W Operating Current                | V <sub>CC</sub> = 5.5V, SK = 1                              |                 | 2.5  | 12                        | mA   |

| V <sub>IL</sub><br>V <sub>IH</sub>                        | Input Voltage Levels                 |                                                             | - 0.1<br>2.0    |      | 0.8<br>V <sub>CC</sub> +1 | V    |

| V <sub>OL</sub><br>V <sub>OH</sub>                        | Output Voltage Levels                | I <sub>OL</sub> = 2.1 mA<br>I <sub>OH</sub> = -400 μA       | 2.4             |      | 0.4                       | v    |

| ILI                                                       | Input Leakage Current                | V <sub>IN</sub> = 5.5V                                      |                 |      | 10                        | μΑ   |

| ILO                                                       | Output Leakage Current               | V <sub>OUT</sub> = 5.5V, CS = 0                             |                 |      | 10                        | μΑ   |

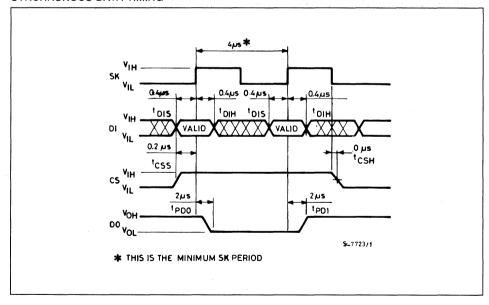

|                                                           | SK Frequency                         | . Ar                                                        | 0               |      | 250                       | kHz  |

|                                                           | SK Duty Cycle                        |                                                             | 25              |      | 75                        | %    |

|                                                           | Input Set-Up and Hold Times:         |                                                             |                 | }    |                           |      |

| t <sub>CSAE</sub><br>t <sub>CSS</sub><br>t <sub>CSH</sub> | CS (Note 2)                          |                                                             | 0.4<br>0.2<br>0 | ·    |                           | μS   |

| t <sub>DIS</sub>                                          | DI                                   |                                                             | 0.4<br>0.4      |      |                           |      |

| t <sub>PD1</sub>                                          | Output<br>DO                         | CL = 100 pF<br>V <sub>OL</sub> = 0.8V, V <sub>OH</sub> = 2V |                 |      | 2                         | μs   |

| t <sub>PD0</sub>                                          |                                      | $V_{IL} = 0.45V, V_{IH} = 2.40V$                            |                 |      | 2                         | -    |

| t <sub>E/W</sub>                                          | Self-Timed Program Cycle             |                                                             |                 |      | 10                        | ms   |

| tcs                                                       | Min CS Low Time (Note 1)             |                                                             | 1               |      |                           | μS   |

| t <sub>SV</sub>                                           | Rising Edge of CS to<br>Status Valid | C <sub>L</sub> = 100 pF                                     |                 |      | 1                         | μ\$  |

| t <sub>OH</sub> , t <sub>1H</sub>                         | Falling Edge of CS to DO tri-state   |                                                             |                 |      | 0.4                       | μ\$  |

Note: 1. CS must be brought low for a minimum of 1 is (tCS) between consecutive instruction cycles.

2. tCSAE condition has to be fullfilled in "WRITE WITH AUTOERASE" mode.

#### **FUNCTIONAL DESCRIPTION**

The input and output pins are controlled by separate serial formats. Eight 9-bit instructions can be executed. The instruction format has a logical "1" as a start bit, two bits as an op code, and six bits of address. The on-chip programming voltage generator allows the user to use a single power supply (V<sub>CC</sub>). It only generates high voltage during the programming modes (write, erase, chip-erase, chipwrite) to prevent spurious programming during other modes.

The programming cycle is self timed, with the data out (DO) pin indicating the ready/busy state of the chip. The serial output (DO) pin is valid as data out during the read mode, and if initiated, as a ready/busy status indicator during a programming cycle. During all other modes the DO pin is in high impedance state eliminating bus contention. The Bulk programming instructions (ERAL, WRAL) are enabled or disabled by the BPE pin. This pin connected to VIH enables the executions of previous mentioned instructions. The BPE pin connected to VIL causes the same instructions to be ignored. If the BPE pin is not connected, it is pulled-up to V<sub>CC</sub> by an on-chip pull-up and the Bulk programming instructions are enabled. Execution of the EWEN, EWDS, WRITE and ERASE instructions are independent from the state of the BPE pin.

# **READ**

The read instruction is the only instruction which outputs serial data on the DO pin. After a READ instruction is received, the instruction and address are decoded, followed by data transfer from the memory register into a 16 bit serial out shift register. A dummy bit (logical "0") precedes the 16 bit data output string. The output data changes during the high state of the system clock.

### ERASE/WRITE ENABLE AND DISABLE

When  $V_{CC}$  is applied to the part it powers up in the programming disable (EWDS) state, programming must be preceded by programming enable (EWEN) instruction. Programming remains enabled until a programming disable (EWDS) instruction is executed or  $V_{CC}$  is removed from the part. The programming disable instruction is provided to protect against accidental data disturb. Execution of a READ instruction is independent of both EWEN and EWDS instructions.

# ERASE (Note 2)

Like most EEPROMs, the register must first be erased (all bits set to logical '1') before the register can be written (certain bits set to logical '0'). After an ERASE instruction is input, CS is dropped low.

This falling edge of CS determines the start of the self-timed programming cycle. If CS is brought high subsequently (after observing the t<sub>CS</sub> specification), the DO pin will indicate the ready/busy status of the chip. The DO pin will go low if the chip is still programming. The DO pin will go high when all bits of the register at the address specified in the instruction have been set to a logical '1'. The part is now ready for the next instruction sequence.

# WRITE (Note 2)

The WRITE instruction is followed by 16 bits of data to be written into the specified address. After the last bit of data (D0) is put on the data in (DI) pin, CS must be brought low before the next rising edge of the SK clock. This falling edge of CS initiates the self-timed programming cycle. Like all programming modes, DO indicates the ready/busy status of the chip if CS is brought high after a minimum of 1  $\mu$ s (tCS). DO=logical '0' indicates that programming is still in progress. DO=logical '1' indicates that the register at the address specifed in the instruction has been written with the data pattern specified in the instruction and the part is ready for another instruction. The register to be written into must have been previously erased.

#### WRITE WITH AUTOERASE (Note 2)

The WRITE instruction is followed by 16 bits of data to be written into the specified address. After the last bit of data (DO) is put on the data in (DI) pin CS must be brought low before the next falling edge of the SK clock.

This falling edge of CS initiates the self-timed programming cycle. Like all programming modes, DO indicates the ready/busy status of the chip if CS is brought high after a minimum of 1  $\mu$ s (t<sub>CS</sub>). DO = logical '0' indicates that programming is still in progress. DO = logical '1' indicates that the register at the address specifed in the instruction has been written with the data pattern specified in the instruction and the part is ready for another instruction.

# FUNCTIONAL DESCRIPTION (Continued)

### CHIP ERASE (Note 2)

Entire chip erasing is provided for ease of programming. Erasing the chip means that all registers in the memory array have each bit set to a logical '1'. Each register is then ready for a WRITE instruction. The chip erase cycle is identical to the erase cycle except for the different op code. The Chip Erase (ERAL) instruction is ignored if the BPE pin is at  $V_{II}$ , i.e. the array data is not changed.

# CHIP WRITE (Note 2)

All registers must be erased before a chip write operation. The chip write cycle is identical to the write cycle except for the different op code. All registers are simultaneously written with the data pattern specified in the instruction. The Chip Write (WRAL) instruction is ignored if the BPE pin is at  $V_{\rm IL}$ , i.e. the array data is not changed.

#### DI/DO

It is possible to connect the Data In and Data Out pins together. However, with this configuration it is possible for a "bus conflict" to occur during the "dummy zero" that precedes the read operation, if  $A_0$  is a logic high level. Under such a condition the voltage level seen at Data Out is undefined and will depend upon the relative impedance of Data Out and the signal source driving  $A_0$ . The higher current sourcing capability of  $A_0$ , the higher voltage at the Data Out pin. To solve this problem the DI pin must be in high impedance after the last rising edge of the SK clock.

#### POWER ON DATA PROTECTION CIRCUITRY

During power-up all modes of operation are inhibited until  $V_{CC}$  has reached a level of between 2.8 and 3.5 volts. During power-down the source data protection circuitry acts to inhibit all modes when  $V_{CC}$  has fallen below the voltage range of 2.8 to 3.5 volts.

Note 1: CS must be brought low for a minimum of 1  $\mu s$  (t<sub>CS</sub>) between consecutive instruction cycles.

**Note 2:** During a programming mode (write, erase, chip erase, chip write), SK clock is only needed while the actual instruction, i.e. start bit, op code, address and data, is being input. It can remain deactivated during the Erase/Write pulse width ( $t_{\rm FW}$ ).

#### **INSTRUCTION SET**

| Instruction   | SB    | Op Code                               | Address      | Data                       | Comments                          |  |

|---------------|-------|---------------------------------------|--------------|----------------------------|-----------------------------------|--|

| READ          | 1 *** | 10                                    | A5A4A3A2A1A0 |                            | Read register A5A4A3A2A1A0        |  |

| WRITE         | 1     | 01                                    | A5A4A3A2A1A0 | D15-D0                     | Write register A5A4A3A2A1A0       |  |

| ERASE         | 1 ,   | 11 - 11 - 11 - 11 - 11 - 11 - 11 - 11 | A5A4A3A2A1A0 | iskiri Milita<br>Karanasan | Erase register A5A4A3A2A1A0       |  |

| WR. AUTOERASE | 1     | 01                                    | A5A4A3A2A1A0 | D15-D0                     | Erase/write register A5A4A3A2A1A0 |  |

| EWEN          | 1     | 00                                    | 11 x x x x   |                            | Erase/write enable                |  |

| EWDS          | 1     | 00                                    | 00 x x x x   |                            | Erase/write disable               |  |

| ERAL          | 1     | 00                                    | 10 x x x x   | ugita in a                 | Erase all registers               |  |

| WRAL          | .1    | 00                                    | 01 x x x x   | D15-D0                     | Write all registers               |  |

M9346 has 8 instructions as shown. Note that the MSB of any given instruction is a "1" and is viewed as a start bit in the interface sequence. The next 8 bits carry the op code and the 6-bit address for 1 of 64, 16-bit registers.

#### **TIMING DIAGRAMS**

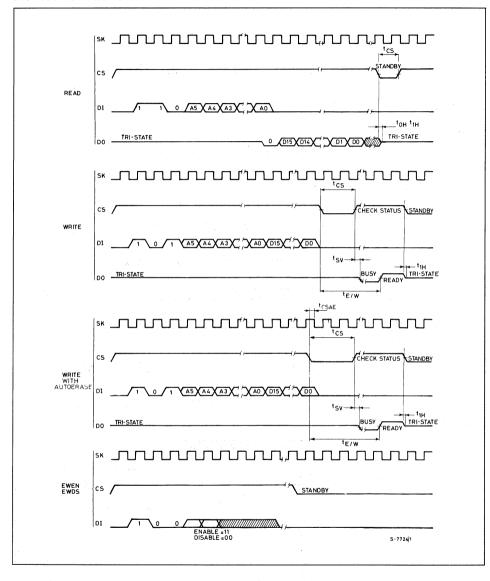

# SYNCHRONOUS DATA TIMING

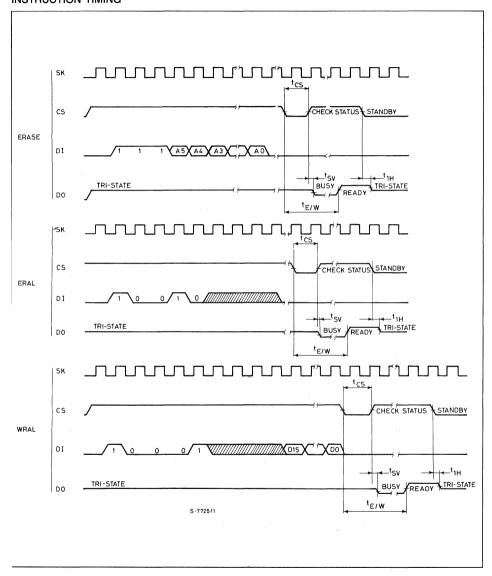

# TIMING DIAGRAMS INSTRUCTION TIMING

# TIMING DIAGRAMS (Continued)

#### INSTRUCTION TIMING

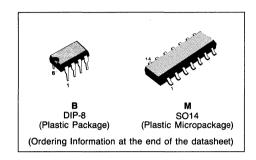

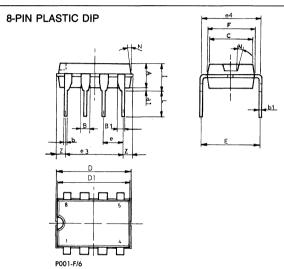

# ORDERING INFORMATION

| Part Number | Max Frequency | Supply Voltage | Temp. Range   | Package |

|-------------|---------------|----------------|---------------|---------|

| M9346B1     | 250 KHz       | 5V ± 10%       | 0° to +70°C   | DIP-8   |

| M9346B6     | 250 KHz       | 5V ± 10%       | -40° to +85°C | DIP-8   |

| M9346M1     | 250 KHz       | 5V ± 10%       | 0° to +70°C   | SO14    |

| M9346M6     | 250 KHz       | 5V ± 10%       | -40° to +85°C | SO14    |

# **PACKAGE MECHANICAL DATA**

|      | mm   |      |      | inches |       |       |

|------|------|------|------|--------|-------|-------|

| Dim. | Min  | Тур  | Max  | Min    | Тур   | Max   |

| Α    |      |      |      |        |       |       |

| a1   | 0.70 |      |      | 0.028  |       |       |

| В    | 1.39 |      | 1.65 | 0.055  |       | 0.065 |

| B1   | 0.91 |      | 1.04 | 0.036  |       | 0.041 |

| b    |      | 0.50 |      |        | 0.02  |       |

| b1   | 0.38 |      | 0.50 | 0.015  |       | 0.020 |

| С    |      |      |      |        |       |       |

| D    |      |      | 9.80 |        |       | 0.386 |

| D1   |      |      |      |        |       |       |

| E    |      | 8.90 |      |        | 0.350 |       |

| е    |      | 2.54 |      |        | 0.100 |       |

| e3   |      | 7.62 |      |        | 0.300 |       |

| e4   |      |      |      |        |       |       |

| F    |      |      | 7.10 |        |       | 0.280 |

| ı    |      |      | 4.80 |        |       | 0.189 |

| L    |      | 3.30 |      |        | 0.130 |       |

| N    |      |      |      |        |       |       |

| Z    | 0.44 |      | 1.60 | 0.017  |       | 0.063 |

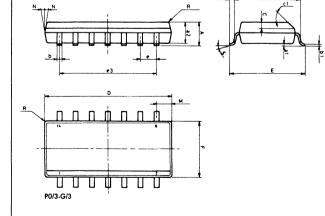

# 14-LEAD PLASTIC MICROPACKAGE

| Dim.             | mm   |      |      | inches |       |       |

|------------------|------|------|------|--------|-------|-------|

|                  | Min  | Тур  | Max  | Min    | Тур   | Max   |

| Α                |      |      | 1.75 |        |       | 0.069 |

| a1               | 0.10 |      | 0.20 | 0.004  |       | 0.008 |

| a2               |      |      | 1.60 |        |       | 0.063 |

| b                | 0.35 |      | 0.46 | 0.014  |       | 0.018 |

| b1               | 0.19 |      | 0.25 | 0.007  |       | 0.010 |

| С                |      | 0.50 |      |        | 0.020 |       |

| <b>c</b> 1       |      | 45°  |      |        | 45°   |       |

| D <sup>(1)</sup> | 8.55 |      | 8.75 | 0.337  |       | 0.344 |

| E                | 5.80 |      | 6.20 | 0.228  |       | 0.244 |

| е                |      | 1.27 |      |        | 0.050 |       |

| e 3              |      | 7.62 |      |        | 0.300 |       |

| F <sup>(1)</sup> | 3.80 |      | 4.00 | 0.150  |       | 0.157 |

| G                | 4.60 |      | 5.30 | 0.181  |       | 0.209 |

| L                | 0.50 |      | 1.27 | 0.020  |       | 0.050 |

| М                |      |      | 0.68 |        |       | 0.027 |

| N                |      |      |      |        |       |       |

| R                |      |      |      |        |       |       |

| S                |      |      | 8°   |        |       | 80    |

**Note:** 1. D and F do not include mold flash or protusions. They should not exceed 0.15 mm/.006 inches.