# Application Manual

Real Time Clock Module RTC-65271

**SEIKO EPSON CORP.**

Copyright Notice

This manual is based on information current as of March, 1994. Note that the contents of this manual are subject to change without notice. Please inquire separately for information concerning product warranties.

#### **Trademarks**

The EPSON® and EPSON logo are registered trademark of Seiko Epson Corporation.

RTC-65271 is a product name of Seiko Epson Corporation.

AT® (PC/AT) is a registered trademark of IBM Corporation.

i386™, i486™ and Pentium™ are registered trademarks of Intel Corporation.

MC146818A is a product name of Motorola Corporation.

DS1287 is a product name of Dallas Semiconductor Corporation.

Rights to other trademarks and product names mentioned in this manual are also acknowledged.

#### Disclaimer

The copyright to this manual is held by Seiko Epson Corporation. Therefore, copying of the contents of this manual without Seiko Epson Corporation's express permission, by whatever method, is prohibited.

This manual neither guarantees any rights in respect of industrial property or other matters, nor is it a commercial title or license.

The example circuits and other components described in this manual in this manual are provided for informational purpose only.

Seiko Epson Corporation cannot bear any responsibility for the implementation of these examples, and you must check circuit behavior independently.

#### Conclusion

We have prepared this manual as carefully as possible. If you find it unsatisfactory or incomplete in any respect, we would welcome your comments.

## RTC-65271 Application Note

This document summarizes frequently asked questions concerning the RTC-65271, which are relevant to both hardware and software design.

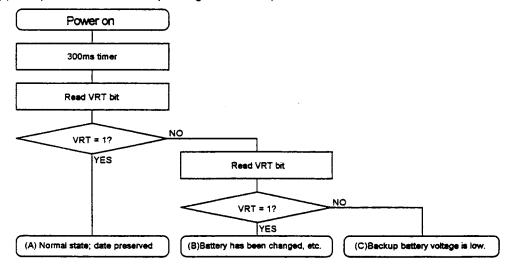

#### Q. What is the function of the VRT bit?

A. The VRT bit in register D reflects the state of the backup batteries. This bit has an internal two-stage latch, indicating the battery state at different times, as follows.

|   | Read       | Significance of VRT bit   |  |  |  |  |  |  |  |  |

|---|------------|---------------------------|--|--|--|--|--|--|--|--|

|   | First      | Battery state throughout  |  |  |  |  |  |  |  |  |

|   | time       | backup phase              |  |  |  |  |  |  |  |  |

| 1 | Second and | Battery state at power on |  |  |  |  |  |  |  |  |

|   | subsequent | time (after backup)       |  |  |  |  |  |  |  |  |

|   | times      |                           |  |  |  |  |  |  |  |  |

- Q. Either data from the chip always reads as 0 or F (hexadecimal) or data read is completely unpredictable. What is the likely cause?

- A. This can happen if the chip select signal is not applied correctly. If the chip select signal is not enabled, the data bus pins are high impedance, and thus if the the data bus lines are stabilized with pull-down or pull-up resistors the values read will always be 0 or FF. If no stabilizing resistors are used, unstable values will result.

- Q. Sometimes the expected data values are read, but sometimes not. What is the likely cause?

- A. This is likely to be caused by a device address conflict. If the same address selects both the RTC and another device, then both may output data to the bus at the same time. If the values happen to agree, then the expected data will be read, but otherwise the value read will depend on which device's output driver happens to be more powerful.

- Q. Clock operation is not maintained properly by the backup batteries. resulting in unexpected register values. What is the likely cause?

- A. When installing the backup batteries it is important not to touch them with bare fingers, as this may transfer dirt or grease and impair the electrical contact with the battery holder. If possible use anti-static gloves when installing. Never use tweezers or other metal implements to handle the

batteries: this is likely to lead to a shortcircuit, and result in dead or unreliable batteries.

## Q. What happens if just one of the backup batteries goes dead?

A. The batteries are connected in parallel in the holder, and therefore should match as closely as possible. Always use two new batteries from the same manufacturer. Otherwise, differences in internal resistance or slight differences in voltage will cause an internal charging current to flow from the stronger battery to the weaker one. As well as wasting the capacity of the stronger battery, this may lead to fluid leakage, as lithium batteries are not generally designed to withstand a charging current.

Using two matching batteries will ensure that they become exhausted at the same time. If, on the other hand, one should become exhausted slightly before the other, the backup function will be maintained provided the total voltage is sufficient.

## Q. Is it possible to use this device without batteries?

A. No. The RTC-65271 is not designed to operate without batteries installed.

The battery terminals have a very high impedance, to provide reliability with a low current consumption. Because of this high impedance, if no batteries are fitted the terminal potentials are unstable, and are subject to noise. Since the noise may make the power supply voltage detection unreliable (because Vod is not stably greater than the battery voltage), affecting operation.

#### Q. What about dead batteries?

A. Yes, the RTC-65271 will operate with dead batteries in place.

As described in the answer to the previous question, the battery terminals are very high impedance, but even dead batteries will have adequate static capacity and internal resistance to stabilize the terminals at a voltage lower than VDD. There will therefore be no operating problems if dead batteries are left in place, except that there is of course no backup function.

- Q. Why should time errors occur during operation, even though the backup function operates correctly?

- A. This is probably either because the power or interface lines are subject to noise, or because of excessively frequent RTC access.

In normal operation, if noise is present on the power supply line (+5 V) or signal lines, and this noise is superimposed on the output from the oscillation circuit, this may cause miscounts in the frequency divider circuits. Epson has implemented as many noise-reduction features in the design as possible, but it is not possible to eliminate the effects of excess noise. Check for sources of noise in the surrounding circuits. If the RTC-65271 is accessed excessively often (upwards of 10 times per second), "switching" will occur in the interface lines and other parts of the circuit. This is a CMOS device, and this switching therefore causes transient currents between Vpp and ground. These may appear on the power supply line as noise, and thus cause miscounts. The output from this device only changes once per second: use appropriate interrupt driven operation so that the RTC is accessed every second or every minute, avoiding surplus accesses.

## Q. What if the clock frequency is not within the specified tolerance?

A. The clock frequency is guaranteed to tolerance at 25°C. If operated at a different temperature the frequency may be affected by the temperature dependence of the quartz crystal. Check the frequency at 25°C.

## Q. If the device does not operate, what are the likely causes?

- A. There are two possible reasons.

- 1. The clock has been stopped in software. The RTC-65271 has a SET bit and DV bits in a control register which stops time counting. If these are set to the "stop" value, the clock will not operate. When powered on, the register values are indefinite, so it is important to ensure that all bits are set appropriately in the initialization procedure.

- The crystal is mechanically damaged. The RTC-65271 uses a 32.768 kHz quartz crystal as the basic oscillating element. If this is subjected to excessive shock or vibration, it may be damaged, preventing the device from operating. The most likely causes of mechanical dropping during the damage are assembly process or vibration. particular, ultrasonic cleaning frequencies close to the oscillating frequency of the crystal; this may cause resonance, and possibly damage. Since the conditions of ultrasonic cleaning are outside Epson's control, users should check carefully before using ultrasonic cleaning.

## **CONTENTS**

|   | Over       | VIEW                                                                  | 1                |

|---|------------|-----------------------------------------------------------------------|------------------|

|   | Bloc       | k Diagram                                                             | 1                |

|   |            | Connections                                                           |                  |

|   |            | Functions                                                             |                  |

|   |            | acteristics                                                           |                  |

|   | 1.         | Absolute Maximum Ratings                                              | 4                |

|   | 2.         | Operating Conditions.                                                 | 4                |

|   | 3.         | Frequency Characteristics                                             | 4                |

|   | 4.         | DC characteristics                                                    | 4<br>1           |

|   |            |                                                                       |                  |

| _ | 1          | Switching Characteristics                                             | ,5<br>-          |

|   | 2          | Switching Characteristics                                             | 5                |

|   | 3.         | Power Supply On/Off TimingAC Characteristics                          | 6                |

| = |            |                                                                       |                  |

|   | negi       | STEC Booker Address Mars                                              | 8                |

|   | 1.         | RTC Register Address Map                                              | 8                |

|   | <u>د</u> . | RTC Register Bit Structure                                            | 8                |

|   | 4          | RTC Register Bit Functions (Summary)                                  | 9                |

|   | 5.         | RAM (RTC and extended RAM)                                            | 10               |

| _ |            |                                                                       |                  |

| = | negi       | ster Functions                                                        | 10               |

|   | 1.         | Indirect Address Register and RTC Data Register                       | 10               |

|   | ۷.         | Clock, Calendar and Alarm Registers                                   | 10               |

|   |            | (1) Time and date registers                                           | 10               |

|   |            | (2) Day-of-the-week register                                          | 11               |

|   |            | (4) Leap year calculation                                             | 11               |

|   | 3.         | Register A.                                                           |                  |

|   |            | (1) RS0, RS1, RS2 and RS3 bits (Rate Selection; read/write; D0 to D3) | 12               |

|   |            | (2) DV0, DV1 and DV2 bits (DiVider selection; read/write; D4 to D6)   | 12               |

|   |            | (3) UIP bit (Update In Progress; read only; D7)                       | 12               |

|   | 4.         | Register B                                                            | 13               |

|   |            | (1) DSE bit (Daylight Saving Enable; read/write; D0)                  | 13               |

|   |            | (2) 24/12 bit (24/12 control; read/write; D1)                         | 13               |

|   |            | (3) DM bit (Data Mode; read/write; D2)                                | 13               |

|   |            | (4) SQWE bit (SQuare Wave Enable; read/write; D3)                     | 13               |

|   |            | (5) UIE bit (Update-completed Interrupt Enable; read/write; D4)       | 14               |

|   |            | (6) AIE bit (Alarm Interrupt Enable; read/write; D5)                  | 14               |

|   |            | (7) PIE bit (Periodic Interrupt Enable; read/write; D6)               | 14               |

|   | 5          | (8) SET bit (SET; read/write; D7)                                     | 14               |

|   | ٥.         | Register C                                                            | 15               |

|   |            | (1) UF bit (Update-completed interrupt Flag; read only; D4)           | 15               |

|   |            | (3) PF bit (Periodic interrupt Flag; read only; D6)                   | 15               |

|   |            | (4) IRQF bit (Interrupt ReQuest Flag; read only; D7)                  | 15<br>4 <i>5</i> |

|   | 6.         | Register D                                                            | 15<br>16         |

|   |            | (1) VRT bit (Valid RAM and Time; read only; D7)                       | 16               |

|   | 7.         | Extended RAM Page Register                                            | 16               |

|   |            | ation Procedure                                                       |                  |

|   | 1          | Clock, Calendar and Alarm Registers                                   | 1 <i>1</i>       |

|   | ••         | (1) Data formats                                                      | 17<br>           |

|   |            | (2) 24/12-hour modes                                                  | /ا<br>ح-∢        |

|   | 2.         | Interrupts                                                            | 1/<br>17         |

|   |            | (1) Interrupt enable bits                                             | 17               |

|   |            | (2) Interrupt status                                                  | 17               |

|   |            | (3) Periodic interrupt.                                               | 17               |

|    |                                                                   | 47 |

|----|-------------------------------------------------------------------|----|

|    | (4) Update-completed interrupt                                    | 17 |

|    | (5) Alarm interrupt                                               | 18 |

|    | (6) Update cycle                                                  | 18 |

|    | 3. Procedure at Power On                                          | 19 |

|    | (1) Settings at initial power on (initialization)                 | 19 |

|    | (2) Data preservation decision on powering on from backup state   | 19 |

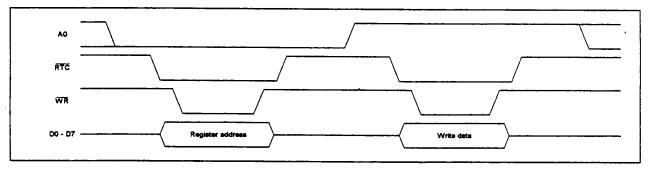

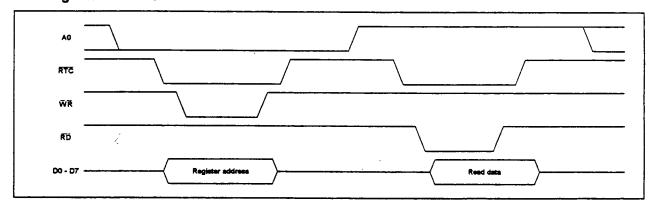

|    | 4. RTC Access                                                     | 20 |

|    | 5. Writing to the RTC                                             | 20 |

|    | 6. Reading from the RTC                                           | 20 |

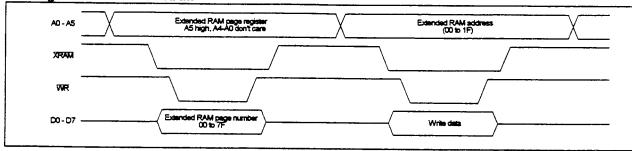

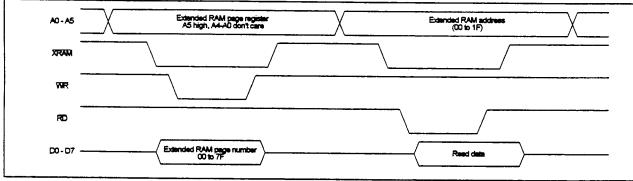

|    | 7. Extended RAM Access                                            | 21 |

|    | 8. Writing to the Extended RAM                                    | 21 |

|    | 9. Reading from the Extended RAM                                  | 21 |

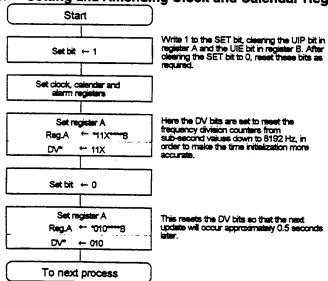

|    | 10. Setting and Amending Clock and Calendar Registers             | 21 |

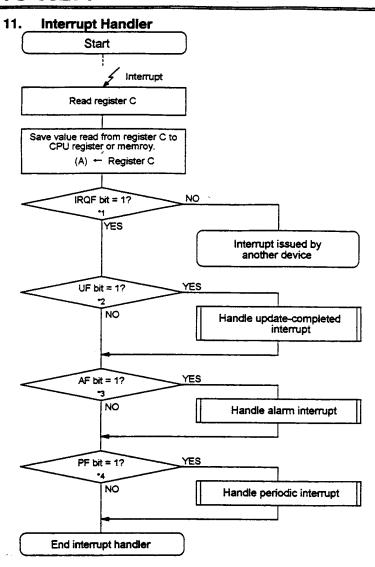

|    | 11 Interrupt Handler                                              | 22 |

|    | 12. Reading the Clock and Calendar Registers                      | 23 |

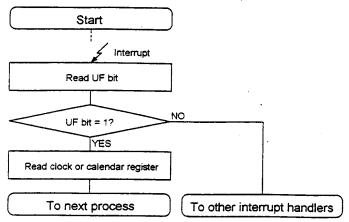

|    | (1) Procedure 1: Using the update-completed interrupt             | 23 |

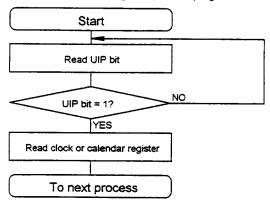

|    | (2) Procedure 2: Monitoring the update-in-progress status bit UIP | 23 |

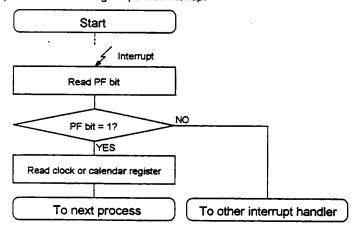

|    | (3) Procedure 3: Using the periodic interrupt                     | 23 |

|    | Example Application                                               |    |

|    |                                                                   |    |

|    | Reference Data                                                    | 24 |

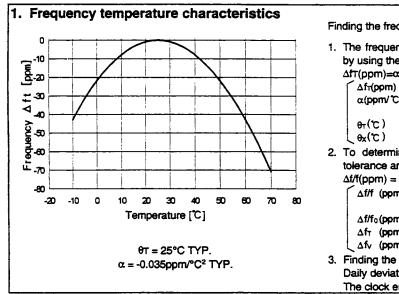

|    | Frequency temperature characteristics                             | 24 |

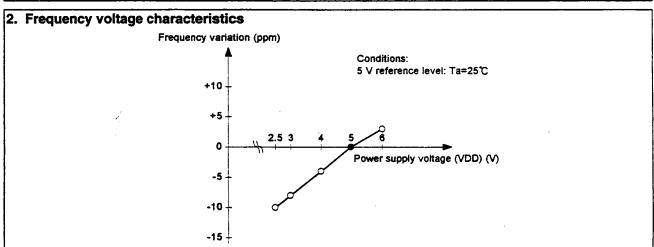

|    | 2. Frequency voltage characteristics                              | 24 |

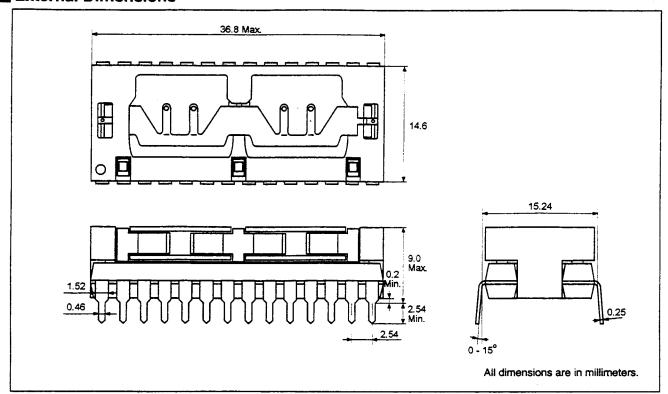

|    | External Dimensions                                               | 25 |

|    |                                                                   |    |

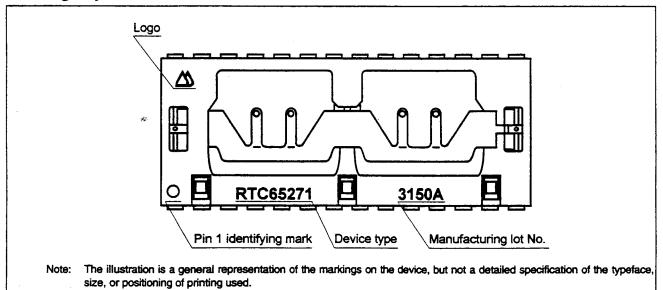

|    | Marking Layout                                                    |    |

|    | Application Notes                                                 |    |

|    | 1. Notes on Handling                                              | 26 |

|    | (1) Avoiding signal lines                                         | 26 |

|    | (2) Bypass capacitor                                              | 26 |

|    | (3) Static electricity                                            | 26 |

|    | (4) Voltage levels of input pins                                  | 26 |

|    | (5) Unused signal pins                                            | 26 |

|    | (6) Condensation                                                  | 26 |

|    | (7) Storage conditions                                            | 26 |

|    | (8) Battery state during operation                                | 26 |

|    | 2. Notes on Mounting                                              | 26 |

|    | (1) Soldering temperature conditions                              | 26 |

|    | (2) Mounting equipment                                            | 26 |

|    | (3) Ultrasonic cleaning                                           | 26 |

|    | (4) Mounting orientation                                          | 26 |

|    | (5) Leakage between pins                                          |    |

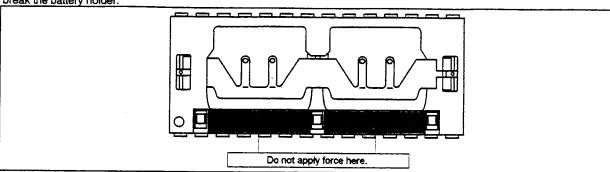

|    | Notes on Battery Holder and Battery Handling                      | 27 |

|    | (1) Batteries used                                                | 27 |

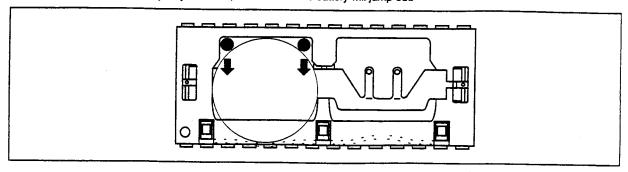

|    | (2) Battery mounting orientation                                  | 27 |

|    | (3) Battery holder                                                | 27 |

|    | (4) Handling the batteries                                        | 27 |

|    | (5) Disposal of used batteries                                    | 27 |

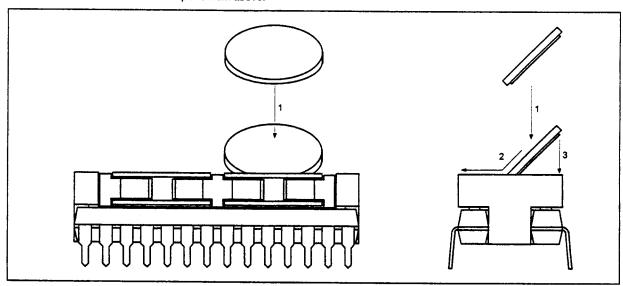

|    | 4. Fitting and Removing Batteries                                 | 2  |

|    | (1) Fitting                                                       | 2  |

|    | (2) Removal                                                       | 28 |

|    | Index                                                             |    |

| 1- | Inday                                                             |    |

## REAL TIME CLOCK WITH S-RAM AND BATTERY HOLDER

## RTC-65271

Built-in quartz crystal for adjustment-free operation and low mounting cost.

Battery holder allows battery replacement. Also supports environmental restrictions.

Ideal for PC/AT® compatible computers.

Internal power supply switching circuit allows automatic backup of both RTC and S-RAM data.

Real time clock is functionally compatible with MC146818A and DS1287.

Indirect address register:

1 byte Clock, alarm and calendar registers: 10 bytes

Control registers:

4 bytes

User RAM:

50 bytes

Extended RAM has 4k bytes of built-in S-RAM

Page register:

RAM configuration:32 bytes x 128 pages = 4k bytes

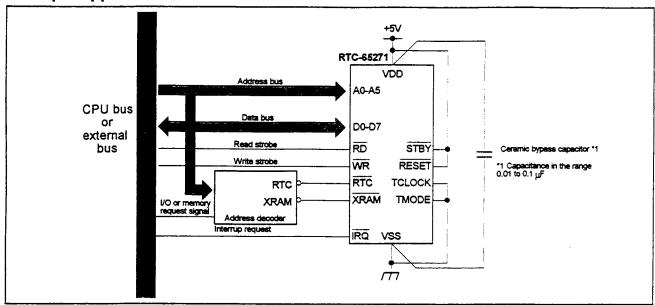

- The adoption of a nonmultiplex bus allows direct connection to a CPU bus or the external bus of an i386™, i486™ or Pentium™ processor.

- Built-in battery protection resistor (UL-compliant).

### Overview

The RTC-65271 is a real time clock module with S-RAM, developed for use in PC/AT® compatible computers and workstations. The builtin quartz crystal provides high accuracy without adjustment, while the absence of any need for external components reduces the cost of incorporation into a system.

The module provides clock and calendar functions, with a daylight saving time function and various periodic reference signal outputs and interrupt functions, and also includes 4k bytes of S-RAM.

Being a C-MOS device, it has a very low power consumption, and the built-in battery holder, together with battery protection resistor and power supply switching function, gives the module an independent fully-automatic backup.

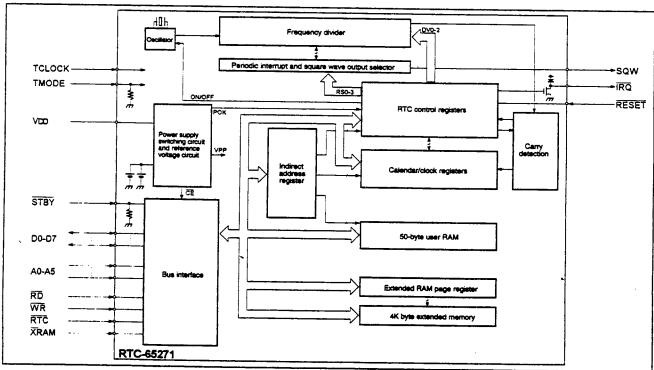

## Block Diagram

## RTC-65271

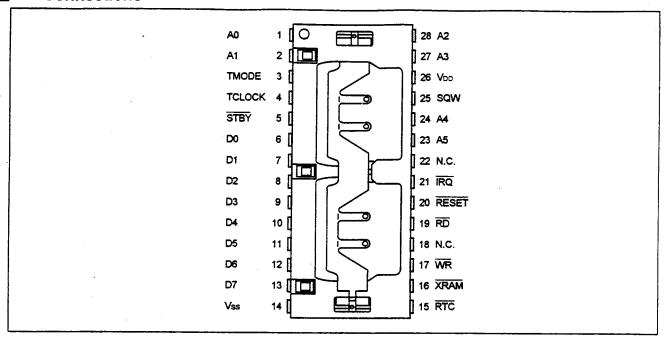

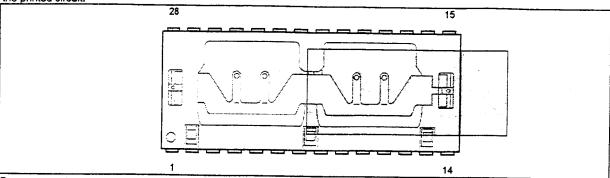

## Pin Connections

## Pin Functions

| Pin names                   | Pin No.            | Input/<br>output   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7<br>(Data bus)         | 6-13               | Bi-<br>directional | The bi-directional data bus can be connected to a CPU data bus, or PC/AT ISA or EISA bus. This but is used for all data transfers from and to internal counters and registers. It accesses calendar and clock data when RTC is low, and extended RAM data when RAM is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A0-A5<br>(Address bus)      | 1,2,23,24<br>27,28 | Input              | The address bus can be connected to a CPU address bus, or to a PC/AT ISA or EISA bus. When RTC is low, it accesses the RTC registers, using A0 to select the indirect address register or RTC dat register. In this case A1 to A5 are ignored.  When A0 is low (address 0), the indirect address register is selected. When A0 is high (address 1 the RTC data register is selected, and the register accessed is determined by the value in the indirect address register.  When RAAM is low the extended RAM can be accessed, and A0 to A5 select the extended RAM address or extended RAM page register.  When A5 is high (addresses 20 to 3F), the extended RAM page register is selected.  When A5 is low (addresses 00 to 1F), the RAM page specified by the extended RAM page register is selected, and A0 to A4 specify the address within that page. |

| WR<br>(WRite)               | 17                 | Input              | The data value present on D0 to D7 is written to the address specified by either arc or xRAM and A0 to A5 on a rising edge on wa.  RD and wa must not be low simultaneously.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RD<br>(ReaD)                | 19                 | Input              | The data value at the address specified by either RTC or XRAM and A0 to A5 is output on D0 to D7 while RD is low.  RD and WR must not be low simultaneously.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| STBY<br>(STand BY)          | 5                  | Input              | When this is low, the device enters the standby state. This inhibits all access, and all outputs are high impedance. Internal clock operation is maintained by the backup battery in the battery holder, and RAM data is also preserved. This pin has an internal pull-down resistor. If not using this pin function, connect to Vpo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RTC<br>(RTC enable)         | 15                 | Input              | When this is low the RTC registers can be accessed.  If both RTC and XRAM are low simultaneously, XRAM takes precedence, and the RTC registers are not selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| XRAM (eXtended RAM enable)  | 16                 | Input              | When this is low the extended RAM can be accessed.  If both RTC and XRAM are low simultaneously, XRAM takes precedence, and the RTC registers are not selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IRQ<br>(Interrupt ReQuest)  | 21                 | Output             | This is an n-channel open drain output, used to issue an interrupt request to the CPU or whatever. In the standby state, or on the backup state, this output is not issued, and the pin remains high impedance. According to the value in register B, this can be used to output an alarm, clock/calenda update completion interrupt, or periodic interrupt.  The load voltage should not exceed Vpp. If the function is not used, leave this pin open-circuit.                                                                                                                                                                                                                                                                                                                                                                                               |

| SQW<br>(SQuare Wave output) | 25                 | Output             | When output is enabled by the SQWE bit in register B, this pin outputs a square wave signal whose frequency is determined by the value in RS0 to RS3 in register A. In the standby state, or on the backup state, there is no output, and the pin remains high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RESET (RESET rtc)           | 20                 |                    | External reset function for RTC. When this pin is low, the RTC registers and signal states become as follows.  Register B bits SQWE, UIE, AIE and PIE, and register C bits UF, AF, PF, and IRQF are all cleared to zero.  The IRQ output goes high impedance.  The bus interface is disabled.  After powering on the RTC, wait at least 300 ms before using this function.  If this function is not used, connect to Vpp.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TCLOCK<br>(Test CLOCK)      | 4                  |                    | This pin is for testing purposes only. If high, device behavior is not guaranteed. Always hold this pir low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TMODE                       | 3                  | Input              | This pin is for testing purposes only. It has an internal pull-down resistor. If high, device behavior is not guaranteed. Always hold this pin low or leave open-circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Voo                         | 26                 |                    | Connect to power supply. For operation, supply between 4.75 V and 5.5 V.  If this voltage falls below VENABLE, writes and reads to the RTC are inhibited. If it falls below Vswrtcuthe power supply to the RTC is switched from this pin to the backup battery. Provided that a backup battery is fitted, timekeeping functions are maintained, and the RAM data is preserved regardless of the voltage on the Voo pin. Connect a 0.01 to 0.1µF bypass capacitor between this pin and GND. To prevent noise problems, make the connection paths as short as possible, and the line impedance as low as possible.                                                                                                                                                                                                                                              |

| GND                         | 14                 |                    | Connect to ground.  Connect a 0.01 to 0.1µF bypass capacitor between this pin and Vpo. To prevent noise problems make the connection paths as short as possible, and the line impedance as low as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| N.C. (No Connection)        | 18,22              |                    | These pins are not used. Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Battery holder

Use type BR-1225 lithium cells. Ensure that the batteries are fitted before powering on the device.

(See pages 19, 26 and 27.)

## RTC-65271

### Characteristics

1. Absolute Maximum Ratings

| Item                  | Symbol | Conditions                              | Min.    | Max.           | Unit        |

|-----------------------|--------|-----------------------------------------|---------|----------------|-------------|

| Power supply voltage  | VDD    | Vpp-Vss                                 | -0.3    | +7.0           | V           |

| Input voltages        | VIN    | Input pins                              | Vss-0.3 | Vpo+0.3        | V           |

| Storage temperature   | TSTG   | Temperature stored as separate item     | -40     | +85            | °C          |

| Soldering temperature | TSOL   | For leads Maximum 260 °C for up to 10 s |         |                | is (package |

| • •                   |        |                                         | m       | aximum 150 °C) | ., -        |

2. Operating Conditions

| Item Symbol           |      | Conditions | Min. | Тур. | Max. | Unit |

|-----------------------|------|------------|------|------|------|------|

| Power supply          | Voo  | Voo-Vss    | 4.75 | 5.0  | 5.5  | >    |

| Operating temperature | TOPR |            | -10  |      | +70  | ပ္   |

Use two type BR1255 batteries for backup.

3. Frequency Characteristics

| item                        | Symbol | Conditions                      | Max. | Unit     |  |

|-----------------------------|--------|---------------------------------|------|----------|--|

| Frequency accuracy          | Δf/fO  | Ta = 25°C; VDO = 5.0 V          | 5±20 | ppm      |  |

| Temperature characteristics | top    | Ta = -10 to 70 °C; VD0 = 5.0 V; | +10  | ppm      |  |

| ·                           |        | 25 °C reference                 | -120 |          |  |

| Voltage characteristics     | fv     | Ta fixed, 5V reference          | ±5   | ppm/V    |  |

| Aging                       | · fa   | Ta = 25 °C; Vpp = 5.0 V         | ±5   | ppm/Year |  |

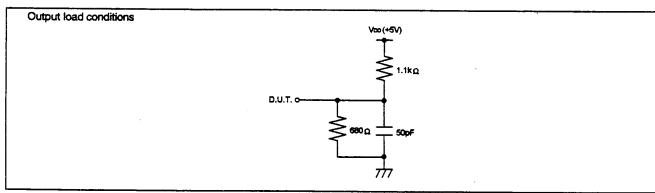

#### 4. DC characteristics

$(VDD = 4.75 \text{ V to } 5.5 \text{ V}, Ta = -10 \text{ to } 70^{\circ}\text{C})$

| Item                                 | Symbol | Conditions                                             | Min. | Тур. | Max.    | Unit |

|--------------------------------------|--------|--------------------------------------------------------|------|------|---------|------|

| Input voltages                       | ViH    |                                                        | 2.2  |      | Vpo+0.3 | ٧    |

| •                                    | ViL_   |                                                        | -0.3 |      | 0.8     | V    |

| Input leakage currents               | IL     | RESET , RD , WR , RTC , XRAM ,<br>D0 - D7, and A0 - A5 |      |      | ±1      | μА   |

| Output voltages                      | Vон    | VD0=5.0V,<br>ILOAD=-4.0mA                              | 2.4  | 70   |         | À    |

|                                      | Val    | VDD=5.0V,<br>ILOAD=4.0mA                               |      |      | 0.4     | ٧    |

| Power supply current consumption     | ipo    | *1                                                     |      |      | 15      | mA   |

| Current in battery backup state IBAT |        | Ta=25°C                                                |      | 0.5  | 1.0     | μA   |

| Current in standby state             | ISTBY  | STBY =VSS                                              |      |      | 2       | μА   |

<sup>\*1</sup> With no load, SQW output 8.192 kHz, no access

## **■** Switching Characteristics

## 1. Switching Characteristics

|                                |        |                    | (VDD= | 4.75V to 5.5V, Ta | =-10 to 70°C) |

|--------------------------------|--------|--------------------|-------|-------------------|---------------|

| <u>Item</u>                    | Symbol | Conditions         | Min.  | Max,              | Unit          |

| Reset pulse width              | tRWL   |                    | 5     |                   | us            |

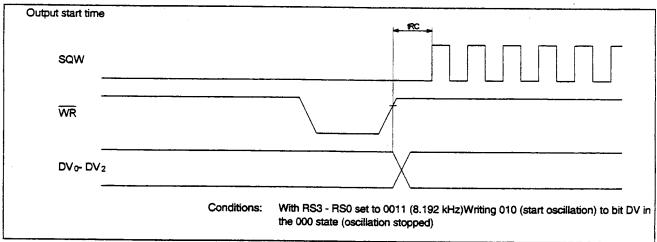

| Oscillation start time         | tRC    | See diagram below. |       | 1                 | s             |

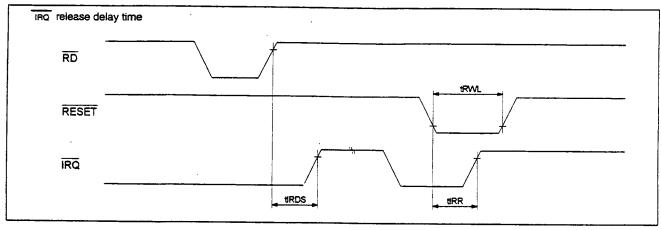

| Release time from RD to IRQ    | tIRDS  |                    |       | 2                 | μs            |

| Release time from RESET to IRQ | tirr   |                    |       | 2                 | μs            |

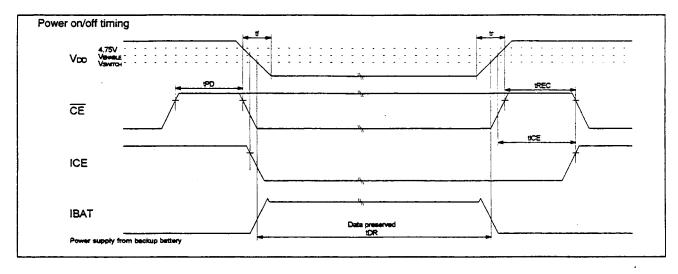

#### 2. Power Supply On/Off Timing

(Ta=-10 to 70°C)

| Item                                                                 | Symbol  | Min.      | Max.      | Unit |

|----------------------------------------------------------------------|---------|-----------|-----------|------|

| Time for c∈ ≥VIH before power off (4.75 V)                           | tPD     | 0         |           | μs   |

| Vdd fall time (4.75 V → 0.0 V, CE ≤ VIH)                             | tf      | 300       |           | µs/V |

| Vdd rise time (0.0 V $\rightarrow$ 4.75 V, $\overline{CE} \le VIH$ ) | tr      | 100       |           | µs/V |

| Invalid time for ce after power on (4.75 V)                          | tREC    | 300       |           | ms   |

| Power supply switching threshold voltage                             | Vswitch | VBAT-0.1  | VBAT+0.3  | V    |

| Chip enable threshold voltage                                        | VENABLE | VBAT×1.25 | VBATX1.35 | ٧    |

| Battery check voltage                                                | VCHECK  | 2.25      | 2.75      | V    |

| ICE rise time after power on                                         | tice    | 20        | 300       | ms   |

CE: External chip enable ( RTC or XRAM )

ICE: Internal chip enable

#### Power on

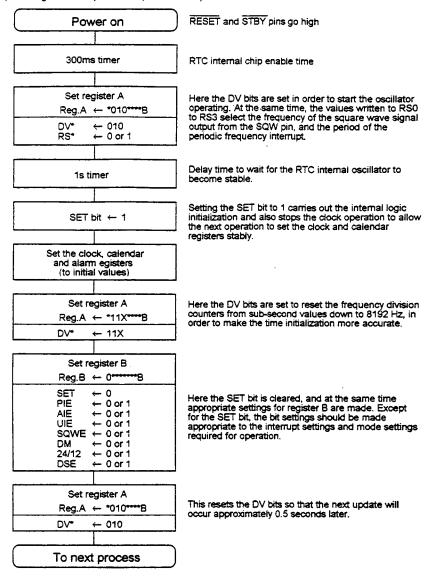

After the power supply is applied to VDD, and this voltage reaches the specified VENABLE level, there is then a delay of 300 ms (tiCE) maximum before the device can be accessed. At this point, if bits DV0 to DV2 of register A are set to specify oscillation stopped, no clock operation takes place. To start the clock it is necessary to set bits DV0 to DV2, and activate the oscillation circuit. When the oscillation circuit is stopped it takes a maximum of one second before the oscillation of built-in quartz crystal stabilizes.

If the voltage supplied to VDD falls below VSWITCH, the power supply switches automatically to the backup battery, and even if VDD falls to zero the clock operations are maintained and the RAM data preserved.

Always ensure that the batteries are fitted before powering on the device.

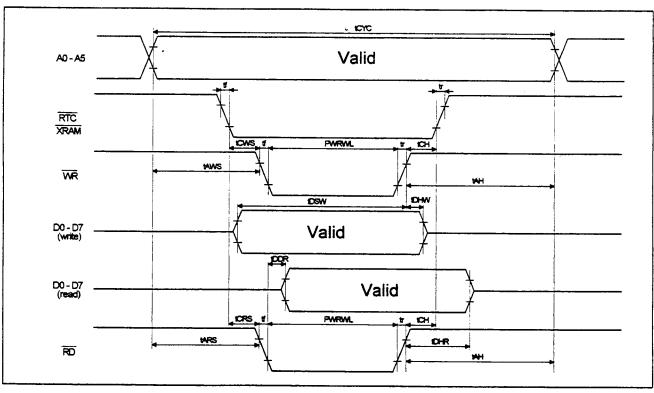

### 3. AC Characteristics

| item                                      | Symbol | Min. | 4.75V to 5.5V, Ta | Unit |

|-------------------------------------------|--------|------|-------------------|------|

| Cycle time                                | tcyc   | 395  | DC                | ns   |

| RD and WR low interval pulse width        | PWRWL  | 325  |                   | ns   |

| cs , RD and WR signal rise and fall times | tr,tf  |      | 30                | ns   |

| Address hold time                         | taH    | 20   |                   | ns   |

| Address set-up time before RD             | tars   | 50   |                   | ns   |

| Address set-up time before wa             | taws   | 0    |                   | ns   |

| Chip select set-up time before RD         | tcrs   | 50   |                   | ns   |

| Chip select set-up time before wa         | tcws   | 0    |                   | ns   |

| Chip select hold time after RD and WR     | tcH    | 20   |                   | ns   |

| Read data hold time                       | tohr   | 10   | 100               | ns   |

| Write data hold time                      | tDHW   | 0    |                   | ns   |

| Delay time from ap to data output         | toor . | 20   | 240               | ns   |

| Write data set-up time                    | tosw   | 200  |                   | ns   |

cs and chip select: external chip select ( RTC or XRAM )

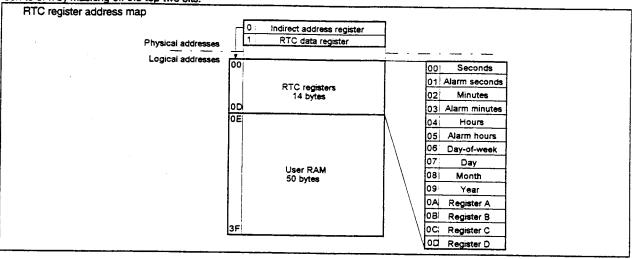

### Registers

This device has two blocks of registers: one for the RTC functions, and one for the extended RAM functions. To access these it is necessary to make RTC low for RTC access and XRAM low for extended RAM access, and set the necessary register or memory address to pins A0 to A5. If both RTC and XRAM are low simultaneously, XRAM takes precedence, and the RTC registers are not selected.

#### 1. RTC Register Address Map

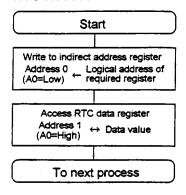

To access an RTC register externally, it is necessary to write the required logical register address in the indirect address register, then carry out the RTC register read or write. When accessing the RTC registers, only A0 of the physical address bits is used.

First, write the logical address of the register to be accessed in the indirect address register. The indirect address register is at physical address 0, so this write is carried out with A0 low. Next, to carry out the read or write to the register at the specified logical address, read to or write from the RTC data register. The RTC data register is at physical address 1, so this read or write is carried out with A0 high.

The internal RTC registers are the same as in the MC146818A and similar devices, with 10 bytes for the clock and calendar registers, 4 bytes of control registers, and 50 bytes of RAM, for a total of 64 logical addresses. Addresses 00h to 3Fh are assigned, but the top two bits are ignored so that these registers are always selected. In other words addresses 40h to FFh are mapped onto addresses 00h to 3Fh by masking off the top two bits.

2. RTC Register Bit Structure

| Address                               | Register         |             |        |        | Data    | bits  |       |       |       | Value                  | Value<br>(BCD)         | Notes           |

|---------------------------------------|------------------|-------------|--------|--------|---------|-------|-------|-------|-------|------------------------|------------------------|-----------------|

| (hexadecimal)                         | name             | D7          | D6     | D5     | D4      | D3    | D2    | D1    | DO    | (binary)               |                        |                 |

| 0                                     | Seconds          | ×           | s40    | s20    | s10     | s8    | 54    | s2    | s1    | 00-3B                  | 0-59                   |                 |

| 1                                     | Alarm<br>seconds | •           | a-s40  | a-s20  | a-s10   | a-\$8 | a-s4  | a-s2  | a-s1  | 00-3B                  | 0-59                   |                 |

| 2                                     | Minutes          | #           | mi40   | mi20   | mi10    | mi8   | mi4   | mi2   | mi1   | 00-3B                  | 0-59                   | <u> </u>        |

| 3                                     | Alarm<br>minutes | •           | a-mi40 | a-mi20 | a-mi10  | a-mi8 | a-mi4 | a-mi2 | a-mi1 | 00-3B                  | 0-59                   |                 |

| 4                                     | Hours            | PM/AM       | #      | #      | h10     | h8    | h4    | h2    | h1    | 01-0C(AM)<br>81-8C(PM) | 01-12(AM)<br>81-92(PM) | 12-hour mode    |

|                                       |                  | #           | #      | h20    | h10     | h8    | h4    | h2    | h1    | 00-17                  | 00-23                  | 24-hour mode    |

| 5                                     | Alarm hours      | a-PM/<br>AM | •      | #      | a-h10   | a-h8  | a-h4  | a-h2  | a-h1  | 01-0C(AM)<br>81-8C(PM) | 01-12(AM)<br>81-92(PM) | 12-hour mode    |

|                                       |                  | •           | •      | a-h20  | a-h10   | a-h8  | a-h4  | a-h2  | a-h1  | 00-17                  | 00-23                  | 24-hour mode    |

| 6                                     | Day-of-week      | #           | #      | #      | #       | #     | w4    | w2    | w1    | 01-07                  | 01-07                  | 24 ROGI III OGE |

| 7                                     | Day              | #           | #      | d20    | d10     | d8    | d4    | d2    | d1    | 01-1F                  | 01-31                  |                 |

| 8                                     | Month            | #           | #      | #      | mo10    | mo8   | mo4   | mo2   | mo1   | 01-0C                  | 01-12                  |                 |

| 9                                     | Year             | y80         | y40    | y20    | y10     | y8    | y4    | y2    | y1    | 00-63                  | 0-99                   |                 |

| Α                                     | Register A       | UIP         | DV2    | DV1    | OVO     | RS3   | RS2   | RS1   | RSO   | -                      |                        |                 |

| В                                     | Register B       | SET         | PIE    | AIE    | UIE     | SQWE  | DM    | 24/12 | DSE   |                        |                        |                 |

| С                                     | Register C       | IRQF        | PF     | AF     | IJΕ     | ×     | ×     | ×     | ×     | _                      | •                      | Read only       |

| D                                     | Register D       | VRT         | ×      | ×      | ×       | ×     | ×     | ×     | ×     |                        |                        | Read only       |

| E                                     |                  |             |        |        |         |       |       |       |       |                        |                        |                 |

| : : : : : : : : : : : : : : : : : : : | RAM              |             |        |        | 50 byte | s RAM |       |       |       | -                      | •                      |                 |

Notes: \* This bit is used for alarm ignore settings. It may be read or written 0 and 1. (See page 11 "Alarm registers" and page 18 "Alarm interrupt".)

# This bit can be read and written as 0 or 1, but 1 should not be written as it results in a non-existent date or time.

x Empty bit. Always reads as 0.

3. RTC Register Bit Functions (Summary)

| Function                                                                                                                                                                                                                           | See page                                                                                                                                                           |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    | 10                                                                                                                                                                 |  |  |  |  |  |  |  |

| Day Sunday Monday Tuesday Wednesday Thursday Friday Saturday                                                                                                                                                                       |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

| the alarm function, write the alarm generation time: there are three registers for hours, minutes and seconds. To use the alarm function, write the alarm generation time to these registers; if any register has bits 6 and 7 set |                                                                                                                                                                    |  |  |  |  |  |  |  |

| to 1, that is, a value of 11xxxxxx binary, that register is ignored in determining whether to issue the alarm.                                                                                                                     | 11                                                                                                                                                                 |  |  |  |  |  |  |  |

| In other words, when the alarm register is set to this ignore code, whatever the value of the corresponding                                                                                                                        |                                                                                                                                                                    |  |  |  |  |  |  |  |

| time register the alarm conditions may still hold. When the alarm conditions for all three values hold, the                                                                                                                        |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    | 12<br>12                                                                                                                                                           |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    | 12                                                                                                                                                                 |  |  |  |  |  |  |  |

| moreover no update will be carried out within the next 244µs.                                                                                                                                                                      |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    | 13                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

| mode, and writing a 0 selects the 12-hour clock mode. When the 24/12 bit is set or changed, the clock                                                                                                                              | 13                                                                                                                                                                 |  |  |  |  |  |  |  |

| registers and clock alarm registers must also be set again. If the settings of the clock registers are                                                                                                                             |                                                                                                                                                                    |  |  |  |  |  |  |  |

| incompatible with the 12/24-hour mode selection the results are unpredictable.                                                                                                                                                     |                                                                                                                                                                    |  |  |  |  |  |  |  |

| This bit selects the representation, binary or BCD, used for the values in the clock, calendar and alarm                                                                                                                           |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

| setting of this bit, it is necessary to rewrite all of the clock, calendar and alarm registers in the new format.                                                                                                                  | 13                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    | 13                                                                                                                                                                 |  |  |  |  |  |  |  |

| SQW low. The frequency of the square wave output is determined by the settings of bits RS0 to RS3.                                                                                                                                 |                                                                                                                                                                    |  |  |  |  |  |  |  |

| This bit controls the update-completed interrupt. Writing a 1 to this bit enables the update-completed                                                                                                                             |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

| disables it. The interrupt is issued at the end of the clock undate cycle when the clock registers are such                                                                                                                        | 14                                                                                                                                                                 |  |  |  |  |  |  |  |

| that the conditions selected by the alarm registers are met.                                                                                                                                                                       | 1-4                                                                                                                                                                |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    | 14                                                                                                                                                                 |  |  |  |  |  |  |  |

| disables it. The periodic interrupt is issued at the frequency determined by the settings of bits RS0 to RS3.                                                                                                                      |                                                                                                                                                                    |  |  |  |  |  |  |  |

| This bit controls RTC updating of registers. Writing a 1 to this bit stops the clock from updating registers,                                                                                                                      |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    | 14                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    | 17                                                                                                                                                                 |  |  |  |  |  |  |  |

| registers, write a 0 to the SET register to restart the normal clock/calendar operation.                                                                                                                                           |                                                                                                                                                                    |  |  |  |  |  |  |  |

| When the RTC is initially powered on, to ensure that internal registers are initialized correctly, always write                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

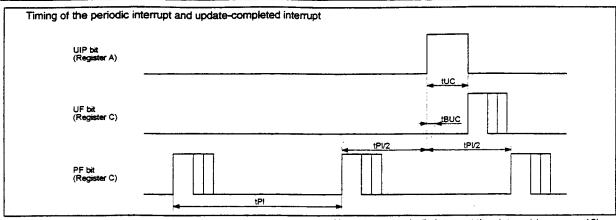

| This bit indicates whether the update-completed interrupt timing has occurred since the UF bit was last                                                                                                                            |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    | 15                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

| UIE bit. This bit is read-only.                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

| This bit indicates whether the alarm interrupt timing has occurred since the AF bit was last read. When its                                                                                                                        |                                                                                                                                                                    |  |  |  |  |  |  |  |

| value is 1, the alarm interrupt timing has occurred, and when it is 0 the timing has not occurred. Reading                                                                                                                         |                                                                                                                                                                    |  |  |  |  |  |  |  |

| ·                                                                                                                                                                                                                                  | 15                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

| Reading this bit automatically clears it.                                                                                                                                                                                          | 15                                                                                                                                                                 |  |  |  |  |  |  |  |

| This bit changes to 1 whenever the interrupt timing occurs, whether or not the interrupt is enabled by the                                                                                                                         |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

| <u> </u>                                                                                                                                                                                                                           |                                                                                                                                                                    |  |  |  |  |  |  |  |

| low. When the IRQF bit is 0 no interrupt has been issued. Reading this bit automatically clears it.                                                                                                                                | 15                                                                                                                                                                 |  |  |  |  |  |  |  |

| This bit is read-only.                                                                                                                                                                                                             |                                                                                                                                                                    |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    |                                                                                                                                                                    |  |  |  |  |  |  |  |

| This bit monitors the state of the backup battery voltage. When the value of the VRT bit is 1, the battery                                                                                                                         |                                                                                                                                                                    |  |  |  |  |  |  |  |

| This bit monitors the state of the backup battery voltage. When the value of the VRT bit is 1, the battery voltage is normal, and when it is 0, the battery voltage has fallen. This bit has an internal two-stage latch:          |                                                                                                                                                                    |  |  |  |  |  |  |  |

| This bit monitors the state of the backup battery voltage. When the value of the VRT bit is 1, the battery                                                                                                                         | 16                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                    | These hold the current date and time, in binary or BCD format as selected by the DM bit. The day-of-thre-week is encoded as shown in the following table.    Value |  |  |  |  |  |  |  |

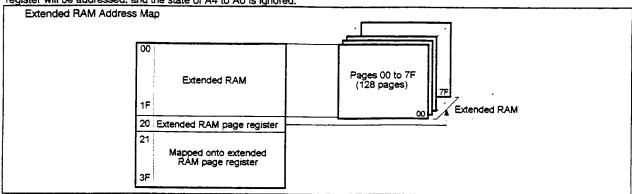

#### 4. Extended RAM Address Map

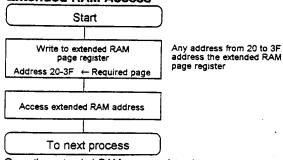

The extended RAM has a 128-page configuration with 32 bytes in each page for a total of 4k bytes. The extended RAM page register specifies a page number within this configuration.

To access an address in the extended RAM, first write the required page number (0 to 127) to the extended RAM page register. The extended RAM page register is accessed at address 20h, but in fact as long as the A5 address line is high the extended RAM page register will be addressed, and the state of A4 to A0 is ignored.

#### 5. RAM (RTC and extended RAM)

The RAM for the RTC and the extended RAM can be read and written freely a byte at a time. The RTC RAM is accessed in the same way as the RTC registers by specifying the address in the indirect address register, then accessing the RTC data register. For the extended RAM, any address can be accessed after specifying the page number in the extended RAM page register (32 bytes per page).

The contents of both areas of RAM are preserved by the backup battery.

During operation, these RAM areas can be accessed at any time, independently of the clock update cycle.

### Register Functions

#### 1. Indirect Address Register and RTC Data Register

The RTC functions of the device use only physical addresses 0 and 1. Access to the internal RTC registers is carried out using the indirect address register and RTC data register.