### SIEMENS

## **Application Note**

#### **Pulse Width Modulator IC SLE 4520**

With the new pulse width modulator (PWM) SLE 4520, it is possible to convert an 8-bit data word into a rectangular signal of corresponding width.

Three independently operating channels with memory, programmable counter and zero detectors are used for this purpose. In combination with a microcontroller (e.g. SAB 8051) and suitable software, pulses can easily be generated to drive three-phase frequency converters with an almost unlimited range of waveforms (sinusoidal, triangular) and any phase relationship. The device can also be used for inverters.

An oscillator with clock output, a programmable prescaler to adapt the switching frequency to the requirements of the output stage, an interlocking stage with status flipflop and the ability to program dead times are features that recommend the SLE 4520 for use in frequency converters to drive three-phase induction motors.

The following report displays the technical possibilities of this design idea, explains the functional operation and discusses the new component's interfaces. Further the use and handling of the new component from both hardware and software sides is shown and the functional operation in combination with the microcontroller SAB 8051 is explained.

#### 1. Principle of function

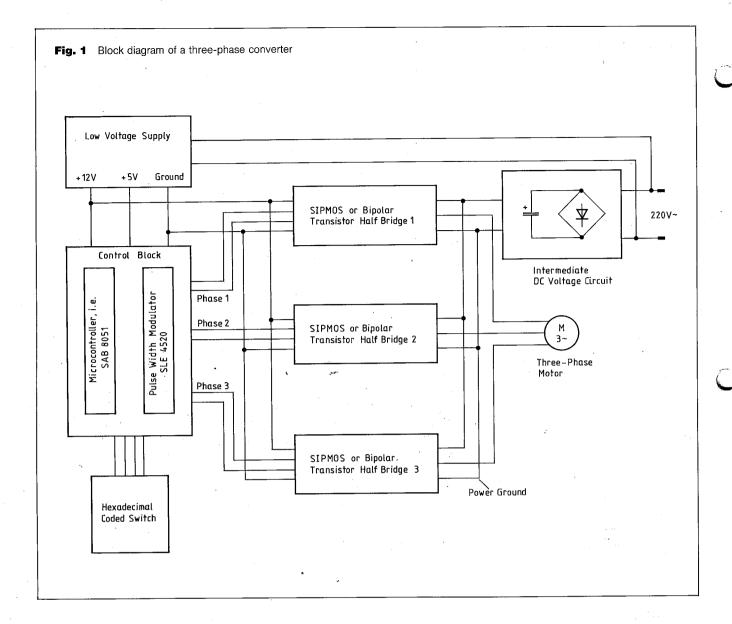

Speed control of three-phase motors is easily done when such motors are supplied with a three-phase voltage the voltage/frequency ratio of which is kept nearly constant with variable frequency. To generate this three-phase voltage a frequency converter is required to rectify and filter the ac supply voltage and subsequently re-convert it into an ac voltage of different frequency by a drive circuit and three power half bridges (Fig. 1). To avoid high losses the output stages operate in a switched mode and are driven by rectangular pulses which increase or decrease in width, depending on the waveform of the sinusoidal function. To produce such pulses with a repetition frequency (switching frequency) up to the limit of the audible range, a drive circuit has proved to be advantageous, which in the simplest case consists of the microcontroller SAB 8051 and the pulse width modulator SLE 4520.

#### 2. Technical feasibility of the system configuration consisting of SAB 8051/SLE 4520 combination

- Generation of three pairs of pulse-width modulated rectangular pulses (phase angle between one phase and the next is, for example, 120°) to drive six individual transistors of an inverter power stage.

- Programmable dead time to safely drive both power switches of a half bridge from

0 to 15  $\cdot \frac{6}{f_{\text{crystal}}}$  or 15  $\cdot \frac{4}{f_{\text{crystal}}}$  in 15 steps. The negative edge is always delayed because the output signal is active LOW.

- Programmable divider in the pulse width modulator to obtain low switching frequencies (bipolar transistor output stages) and at the same time to operate the microcontroller at higher crystal frequencies.

- Direct drive of an optocoupler interface to isolate control and load circuits (I<sub>sink</sub> = 20 mA maximum).

- All six outputs of the SLE 4520 are set to HIGH level either dynamically by an inhibit signal (INHIBIT) or statically by an R-S flipflop (SET STATUS). Thus blocking of all six individual transistors of the power circuit is possible.

- DC braking is possible by selecting different fixed duty cycles on the three output pairs.

- Direction of rotation is reversed by software by exchanging two phases.

- Sine-wave frequency range between approx. 0 Hz and 2600 Hz.

- Switching frequency range between 1 kHz and 20 kHz. -

- Resolution of desired sine-wave function:

8 bits with a switching frequency of  $\frac{f_{\text{crystal}}}{6 \cdot 2^8}$  or

7 bits with a switching frequency of  $\frac{f_{\text{crystal}}}{6 \cdot 2^7}$

Example: With a resolution of 7 bits and a crystal frequency of  $f_{\rm crystal}=12$  MHz a switching frequency of 15.6 kHz results.

- The smallest change in the pulse width is 333 ns with  $f_{\text{crystal}} = 12 \text{ MHz}$  and divider ratio 1:4.

- Changing the switching frequency cycle in 1-μs steps allows the transition from one sine-wave frequency stage to the next quasi continuously (virtually analog).

- Evaluating the bit pattern at one port of the microcontroller SAB 8051 enables many (256) different speed control programs to be selected.

- Output frequency amplitudes are allocated by filing a corresponding table in the program (table size = number of steps × 3) or by linking a table to the output values of an A/D converter.

- Low current consumption of the pulse width modulator because of ACMOS technology.

# 3. Description of the functional blocks of the pulse width modulator (PWM) SLE 4520

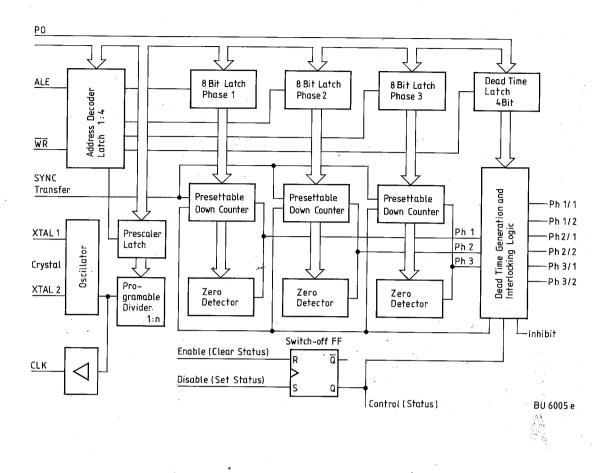

After listing the technical possibilities the substantial functional blocks of the PWM **(Fig. 2)** are described, based on a combination with the microcontroller SAB 8051 and an in-house developed program. However, in principle other hardware and software combinations can be used as well.

#### 3.1 On-chip oscillator

As oscillations from the crystal of the microcontroller do not permit further processing by digital circuits, an oscillator is integrated on the PWM. This feeds the programmable prescaler and has a buffered output for the connected microcontroller. Additional capacitors at the crystal terminals become unnecessary.

#### 3.2 Interface to the microcontroller

Data from the SAB 8051 microcontroller to the SLE 4520 pulse width modulator are transferred via the data bus P0 using control signals ALE and WR. Three 8-bit registers for the three phases and two 4-bit registers to preset dead time and prescaler ratios, as well as an address decoder latch to buffer particular addresses, are connected to the data bus of the SLE 4520.

Transmission of a value is initiated by the instruction MOVX @R0, A (SAB 8051) with the external address being loaded into the R0 register and the data value to be transferred in the accumulator.

Fig. 2 Block diagram of pulse width modulator SLE 4520

Allocations are as follows:

| Register                                            |                                                                                                             |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 8-bit register for phase 1                          |                                                                                                             |

|                                                     |                                                                                                             |

| dead time control register divider control register |                                                                                                             |

|                                                     | 8-bit register for phase 1 8-bit register for phase 2 8-bit register for phase 3 dead time control register |

The last two registers have to be written only once when initialized. In the case of a controller output the above mentioned 3-bit address is latched and decoded with the falling edge of the ALE clock. With the rising edge of the WR signal data are loaded from the bus into the registers of the pulse width modulator.

#### 3.3 Divider control register

The desired divider ratio is set with the divider control register. Hence, the divider control register is loaded in the initial routine with an appropriate value to produce low switching frequencies with a simultaneously high microcontroller operating frequency. Allocation of the value in the divider register, with which the operating frequency of the SLE 4520 is selected, is shown in **Table 1**.

**Table 1** Allocation of value and divider ratio

| Value | Divider ratio down counter | Divider ratio<br>delay clock |

|-------|----------------------------|------------------------------|

| 0     | 1:4                        | 1;4                          |

| 1     | 1:6                        | 1:6                          |

| 2     | 1:8                        | 1:4                          |

| 3     | 1:12                       | 1:6                          |

| 4     | 1:16                       | 1:4                          |

| 5     | 1:24                       | 1:6                          |

| 6     | 1:32                       | 1:4                          |

| 7     | 1:48                       | 1:6                          |

The switching cycle (run time of the timer 0, determined by the initial value in the auto-reload registers TH0 of the microcontroller) should be selected after the divider ratio for the down counter is fixed so as to barely reach the maximum pulse width. This means that with a PWM counter operating clock of, say, 1 MHz (oscillator frequency of 12 MHz, divider ratio 1:12) and a table value of 127 (7 bits) the counter reaches zero after 128  $\mu$ s. Reload register TH0 for timer 0 in the microcontroller has to be written in this case with 80 H (switching frequency cycle 128  $\mu$ s).

**Table 2** gives the useful allocation of counter and switching frequencies for the SAB 8051 (12 MHz crystal).

**Table 2** Allocation of counter and switching frequency of SAB 8051

| Divider ratio down counter | Counter<br>frequency             | Run time<br>Timer 0                 | Switching frequency                        | Reso-<br>lution                  |

|----------------------------|----------------------------------|-------------------------------------|--------------------------------------------|----------------------------------|

| 1:6<br>1:6<br>1:12         | 2 MHz<br>2 MHz<br>1 MHz<br>1 MHz | 64 μs<br>128 μs<br>128 μs<br>256 μs | 15.6 kHz<br>7.8 kHz<br>7.8 kHz<br>3.9 kHz  | 7-bit<br>8-bit<br>7-bit<br>8-bit |

| 1:24<br>1:24<br>1:48       | 500 kHz<br>500 kHz<br>250 kHz    | 256 μs<br>2×256 μs<br>2×256 μs      | 3.9 kHz<br>3.9 kHz<br>1.95 kHz<br>1.95 kHz | 7-bit<br>8-bit<br>7-bit          |

| 1:48                       | 250 kHz                          | 4×256 μs                            | 975.0 Hz                                   | 8-bit                            |

#### 3.4 Conversion of data word into pulse width

Pulse generation in the three processing channels is done by a presettable 8-bit down counter and a zero detector (OR gate) which is connected to the eight counter outputs. With the transfer pulse from the microcontroller (width is one instruction cycle) the repetition rate of which determines the switching frequency, the presettable counter is loaded with the contents of the appropriate register and a 1 appears at the zero detector's output (provided the register does not contain 00H).

This 1 digit enables the counter to count down. When zero is reached the pulse ends and the counter is stopped until the next transfer pulse arrives. The crystal frequency multiplied by the divider ratio clocks the PWM down counter.

### 3.5 Dead time control register and dead time generation

Each half bridge contains two transistors. The dead time is defined as the period of time between the conducting state of one transistor in a half bridge and the blocking state of the other transistor and vice versa.

The dead time between the drive pulses for the two transistors of a half bridge should take into account the storage times of the bipolar driver and power transistors to prevent dangerous overlapping of switching operations ("shoot-trough"). In the pulse width modulator, the dead time is obtained by linking the pulse-width-modulated source signal logically with a delayed signal. The delay is obtained by passing the source signal through a 15-bit shift register with 15 outputs. The shift pulse is either

$$\frac{f_{\text{crystal}}}{6}$$

or  $\frac{f_{\text{crystal}}}{4}$

(depending on the contents of the divider control register, according to table 1).

To select the delay and thus the dead time only one output of the shift register needs to be addressed and then switched through to the logic circuit. This is provided by three 1:16 multiplexers.

15 dead times are presettable (incl. zero dead time) by writing a value between 0 and 0FH into the appropriate control register.

The dead time depends on the crystal frequency and the preset divider ratio of the delay clock (1:4 od 1:6). For a 12-MHz crystal frequency the following dead times apply:

**Table 3** Dead times set in the dead time control register with divider ratios of 1:4 and 1:6

| Word in dead time memory | Dead time [µs] at divider ratio |     |  |

|--------------------------|---------------------------------|-----|--|

| dead time memory         | 1.7                             | 1.0 |  |

| 0                        | 0                               | 0   |  |

| 1                        | 0.33                            | 0.5 |  |

| 2                        | 0.66                            | 1   |  |

| 3                        | 1.0                             | 1.5 |  |

| 4                        | 1.33                            | 2   |  |

| 5                        | 1.66                            | 2.5 |  |

| 6                        | 2.0                             | 3   |  |

| 7                        | 2.33                            | 3.5 |  |

| 8                        | 2.66                            | 4   |  |

| 9                        | 3.0                             | 4.5 |  |

| 10                       | 3.33                            | 5   |  |

| 11                       | 3.66                            | 5.5 |  |

| 12                       | 4.0                             | 6   |  |

| 13                       | 4.33                            | 6.5 |  |

| 14                       | 4.66                            | 7   |  |

| 15                       | 5.0                             | 7.5 |  |

#### 3.6 Interface to the power stage

The interface to the power stage is provided by outputs Ph 1/1 to Ph 3/2. Without dead time Ph 1/2 is inverted to Ph 1/1, Ph 2/2 to Ph 2/1 and Ph 3/2 to Ph 3/1. The active switching state is LOW.

With a programmed dead time the negative edges of the output signal are shifted to the right by the period of the dead time.

The outputs are capable of directly driving TTL devices or optocouplers for voltage isolation of the drive block from the power stage with a current of up to 20 mA.

#### 3.7 Interlocking of the outputs

All six outputs can be set to HIGH level during the inhibit signal (pin 19). Hence the light emitting diodes of the connected optocouplers are currentless and all six individual transistors of the power circuit are blocked. This option is particularly useful when switching on the drive block as clean pulses at the pulse width modulator output are available only after the start up of the oscillator and the initialization routine has been executed.

As the SAB 8051 sets the port outputs to HIGH on switching, only one pin of the microcontroller port needs to be connected to inhibit. At the end of the initialization routine this port pin is set to LOW.

Another way of inhibiting the outputs (hold function) is to apply a High pulse to the SET input (pin 22) of the status flipflop. This inhibit state is indicated by the "Status" output (pin 20) and can be used to indicate or inform the microcontroller (active High; used, for example, in the event of power failure, short circuit, excess temperature etc.). The status flipflop is cleared by a High pulse at the "Clear Status" input (pin 21).

#### 4. Application examples

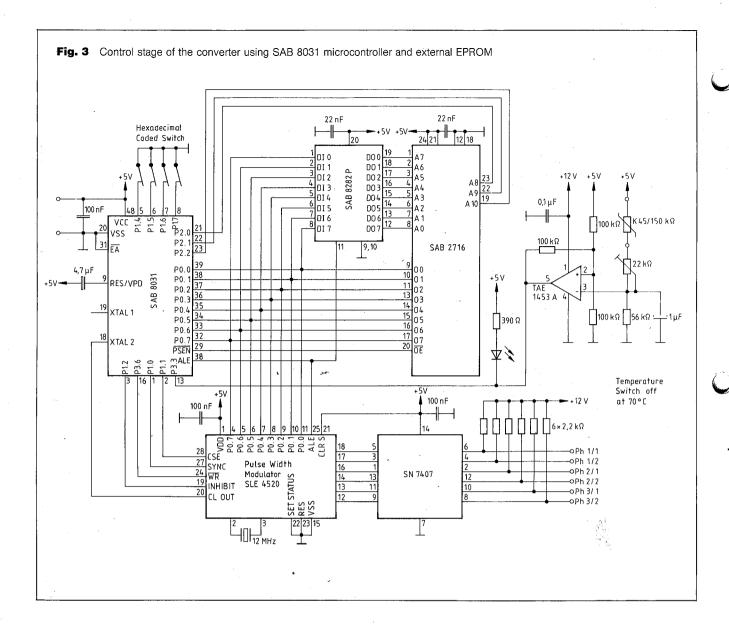

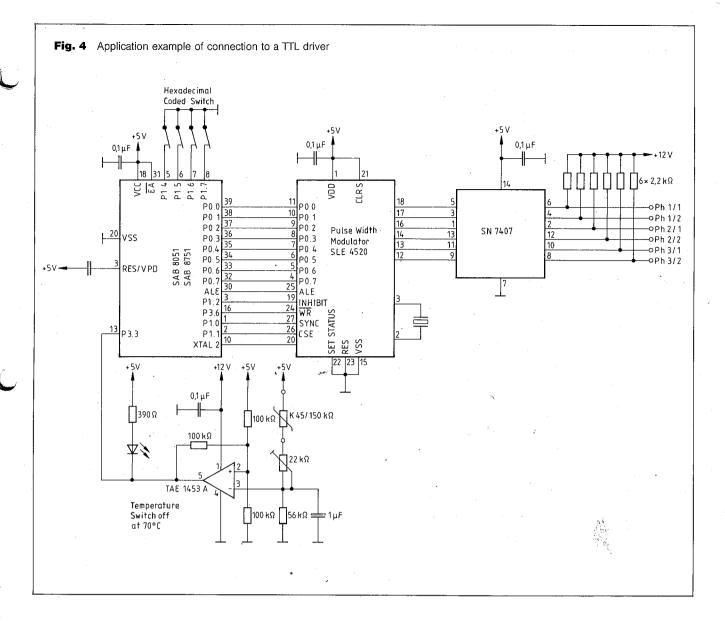

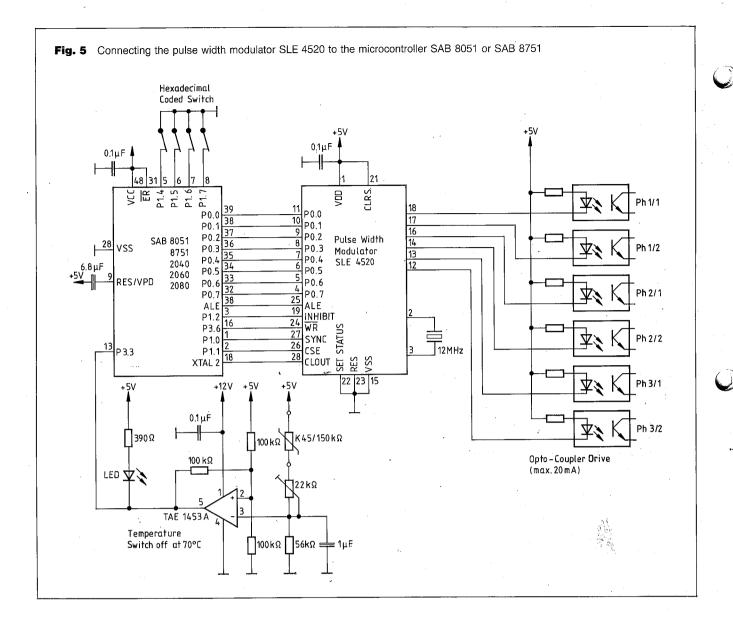

**Figs. 3 through 5** show how the PWM SLE 4520 should be connected to the ROMless microcontroller SAB 8031, or the EPROM version SAB 8751 or to the mask-programmable version SAB 8051.

Unused inputs must be set to defined levels (HIGH or LOW), as the SLE 4520 is a CMOS device.

## 5. Initialization of the drive block (see listing 1)

The initialization routine is started with a jump instruction at the beginning of the program. Subsequently the vector addresses for the four interrupts are allocated and — if required — identified with the branch destination. During the initialization routine the applied registers are set to a starting value and the stack register and the operating mode of timer 0 and timer 1 are defined.

The number 12 H in the TMOD register indicates that the timer 1 will operate as a 16-bit timer and timer 0 as an 8-bit timer in the auto reload mode.

By writing 8EH into the IE register the interrupt sources timer 0, timer 1, and the external interrupt 1 are enabled individually or simultaneously. High priority is assigned to the interrupt of timer 0 and the external interrupt INT1 by setting PX1 and PT0 in the IP register. Subsequently, the registers in the PWM for the three phases, for the dead time and the divider ratios, for the down counter and the delay clock will be addressed and written.

After the DPT has been loaded with the initial value of the table address for amplitude 0, the registers 10 H and 11 H have received an initial value, and the debounce and reset flags are set, the subroutine "SABFR" (interrogation of switch) is implemented in order to determine and evaluate the switch status. The auto reload register TH0 for timer 0 is then loaded with the number which corresponds to the switching frequency cycle (0C0H =  $64~\mu s$ ). The low byte of timer 0, on the other hand, is loaded with a number for rapid overflow and the TCON register is written.

The number 55 H indicates that timer 0 and timer 1 will start and that an edge interrupt has been provided for the external interrupt INT1.

The last instruction enables the PWM, since in our example P1.2 has been connected to RES1.

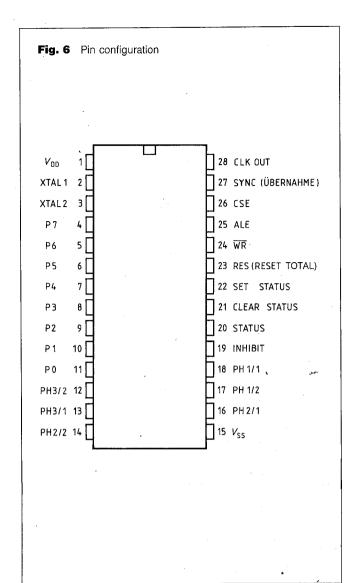

| <b>7.</b>                         | . Pin description                                 |                                                                                                                            |  |  |

|-----------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN                               | Description                                       | Function                                                                                                                   |  |  |

| 1 2 3 4                           | V <sub>DD</sub><br>XTAL1<br>XTAL2<br>P7           | + 5 V connection Crystal connection Crystal connection                                                                     |  |  |

| 5<br>6<br>7<br>8<br>9<br>10<br>11 | P6<br>P5<br>P4<br>P3<br>P2<br>P1<br>P0            | Data bus connections (inputs)                                                                                              |  |  |

| 12<br>13                          | PH3/2<br>PH3/1                                    | Output phase 3 inverted Output phase 3 normal (active low)                                                                 |  |  |

| 14<br>15<br>16                    | PH2/2<br>V <sub>ss</sub><br>PH2/1                 | Output phase 2 inverted<br>Ground connection<br>Output phase 2 normal                                                      |  |  |

| 17<br>18                          | PH1/2<br>PH1/1                                    | (active low) Output phase 1 inverted Output phase 1 normal (active low)                                                    |  |  |

| 19                                | INHIBIT                                           | Inhibit (active high) sets all phase outputs to H                                                                          |  |  |

| 20<br>21<br>22<br>23<br>24        | STATUS<br>CLEAR STATUS<br>SET STATUS<br>RES<br>WR | Status of status flipflop Resets status flipflop Sets status flipflop Chip reset Input for WR pulse from micro- controller |  |  |

| 25                                | ALE ·                                             | Input for ALE clock from micro-<br>controller                                                                              |  |  |

| 26<br>27                          | CSE<br>SYNC                                       | Controller Chip select Input for transfer pulse from microcontroller                                                       |  |  |

| 28                                | CLK OUT                                           | OUTPUT crystal frequency for microcontroller                                                                               |  |  |

#### 6. Table access and output based on the SAB 8051 example (listing 2)

Two registers and the DPT register are required for a continuous output of the table values to the phase registers of the connected PWM.

The required command sequence is as follows: MOV R0, # address phase register MOV A, R4 MOVC A, @ A + DPTR MOVX@R0, A

To generate the table address, the table value counter R4 is added as index to the table start address contained in the DPT register.

By incrementing R0 and R4 the above command sequence fetches and transfers the values for phase 1 through 3. It is therefore required that the values for phase 1 through 3 for a certain angle are listed in successive order in the table.

The table therefore lists triple the number of steps.

#### Listing 1

:Initialization

|                                                       | CSEG AT 0 SJMP INIT ORG 03H ORG 0BH AJMP TINTO ORG 013H ORG 01BH AJMP TINT1 ORG 26H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ;START WITH EXT. INTERRUPT INTO ;START WITH TIMER 0 INTERRUPT ;TIMER 0 INTERRUPT ROUTINE  ;START WITH EXT. INTERRUPT INT1 ;START WITH TIMER 1 INTERRUPT ;TIMER 1 INTERRUPT ROUTINE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT: CLR CLR MOV | 21H,A R0,A R1,A R2,A R3,A R4,A R5,A R6,#01H R7,#01H SP,#STACK_START TMOD,#00010010 @ IE,#1010000B IE,#11100000B IE,#11100000B IE,#11100000B IE,#11100000B IE,#1001110B IP,#11100000B IE,#1001110B IP,#11100000B IE,#10001110B IP,#11100000B IE,#10001110B IP,#11100000B IE,#10001110B IP,#11100000B IE,#100D IM,#00D IM,#00D IM,#00D IM,#1GH TABLE0 IM,#10D IM | ¡FOR TEST PURPOSES ;REGISTER INITIALIZATION ;CLEAR FLAG 0 TO 7 ;CLEAR FLAG 8 TO 15 ;ADDRESS REGISTERS FOR THE 3 PHASES ;LATCH FOR STARTING ADDRESS OF TABLE ; ;COMPARE REGISTER FOR BCD SWITCH ;STEP COUNTER ;SET DEBOUNCE COUNTER FOR "DECIDE" ;PREPARE COUNTER FOR PULSES PER STEP ;OPERATING MODE TIMER 0, TIMER 1 ;CLEAR PRIORITY INTERRUPT ;ENABLE INTERRUPT FOR TO, T1, INT1 ;CLEAR PRIORITY FOR TO, T1, INT1 ;CLEAR INTERRUPT FOR TO, T1, INT1 ;HIGHEST PRIORITY FOR IMER 0 ;PULSE DUTY FACTOR 1:1 ;WRITE PHASE REGISTER 1 ;INCREMENT EXT. ADDRESS ;WRITE PHASE REGISTER 2 ;PHASE REGISTER 3 ;ADDRESS DEAD TIME LATCH ;WRITE DEAD TIME LATCH ;WRITE DEAD TIME LATCH ;WRITE DIVIDER LATCH ;AMPLITUDE 0 ;10 VALUES ARE PROCESSED ;ARBITRARY STARTING VALUE  ;BIT FOR DECIDING CALL OR INT. ;SWITCH INTERROGATION ;SWITCHING FREQUENCY PERIOD = 64 μS ;FOR ACCELERATED TO OVERFLOW ;EDGE INTERRUPT FOR INT1, T0, T1 START ;ENABLE PWM |

#### Listing 2

Output routine for phases 1 to 3 with change in direction

New values for amplitude, sinusoidal frequency, number of steps/period pulses/steps are transferred at the end of a period in the "NLOAD" section.

| ;Interrup                | t                                                                                                                                   |                                                                                                         | service routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                          |                                                                                                                                     | RSEG                                                                                                    | ;OUTPUT SEGMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| TINTO:                   | SETB<br>CLR<br>PUSH<br>PUSH<br>CLR<br>DJNZ<br>MOV                                                                                   | P1.0<br>P1.0<br>PSW<br>ACC<br>IE.7<br>R7, OVER<br>R7, 10H                                               | ;PULSE FOR EXT. HARDWARE ;END OF PULSE ;SAVE PSW OF MAIN PROGRAM ;AS WELL AS ACCU ;INHIBIT INTERRUPT ;WHEN COUNTER =0 OUTPUT, OTHERWISE OVER ;TRANSFER CONTENTS OF 10 TO REG. R7                                                                                                                                                                                                                                                                                                                               |    |

|                          | JB                                                                                                                                  | Rwech_flag,RWECH                                                                                        | ;WITH FLAG=1 CHANGE IN DIRECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| OUT                      | FPUT OF 3-P MOV MOV MOVC MOVX INC INC MOV MOVC MOVX INC INC MOV MOVC MOVX INC INC NC INC MOV MOVC MOV MOVC MOV MOVC MOV MOV NOP NOP | HASE VALUE                                                                                              | ;SET ADDRESS COUNTER FOR EXT. REG. TO ZERO ;LOAD TABLE INDEX INTO ACCU ;FETCH SUPPORT VALUE PHASE 1 FROM TABLE ;OUTPUT SUPPORT VALUE TO PHREG. 1 ;INCREMENT ADDRESS COUNTER FOR 2ND PHASE ;INCREMENT TABLE INDEX ;FETCH TABLE INDEX ;FETCH SUPPORT VALUE PHASE 2 FROM TABLE ;OUTPUT SUPPORT VALUE TO PHREG. 2 ;INCREMENT ADDRESS COUNTER FOR 3RD PHASE ;INCREMENT TABLE INDEX ;FETCH TABLE INDEX ;FETCH SUPPORT VALUE PHASE 3 FROM TABLE ;OUTPUT SUPPORT VALUE PHREG. 3 ;TIME COMPENSATION FOR OTHER DIRECTION |    |

| ;<br>ABFR:               | INC<br>MOV<br>CJNE                                                                                                                  | R4<br>A,R4<br>A,11H,OVER                                                                                | ;INCREMENT TABLE INDEX<br>;FETCH TABLE INDEX<br>;HAVE ALL STEPS BEEN PROCESSED?                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| NLOAD:                   | DEC JNB MOV MOV MOV MOV CLR JNB SETB SJMP                                                                                           | 09H Ueber flag,AWERT 10H,12H 11H,13H TH0,14H DPL,R2 DPH,R1 Ueber_flag Aender_flag,FORT Rwech_flag AWERT | ;TIME COUNTER-1 ;NO NEW VALUE WHEN FLAG = 0 ;AFTER SWITCH HAS BEEN QUERIED ;VALUE IS TRANSFERRED IN ZERO CROSSOVER ;TRANSFER OF NEW SWITCHING FREQUENCY ;TRANSFER OF TABLE ;START ADDRESS ;CLEAR TRANSFER FLAG ;FLAG FOR CHANGE IN DIRECTION ;SET DIRECTIONAL FLAG                                                                                                                                                                                                                                             | ٠. |

| FORT:<br>AWERT:<br>OVER: | CLR<br>MOV<br>SETB<br>POP<br>POP<br>RET!                                                                                            | RWENT<br>RWech_flag<br>R4,#00H<br>IE.7<br>ACC<br>PSW                                                    | ;SET STEP COUNTER TO ZERO<br>;ENABLE INTERRUPT<br>;TRANSFER ACCU<br>;AND PSW                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| ; PRO<br>RWECH:          | OGRÁM SEC<br>MOV<br>MOV                                                                                                             | TION FOR DIRECTION<br>R0,#2H<br>A,R4                                                                    | ;SET ADDRESS COUNTER EXT. REGISTER TO 2<br>;TABLE INDEX                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|                          | MOVC<br>MOVX<br>DEC<br>INC                                                                                                          | A,@A+DPTR<br>@R0,A<br>R0<br>R4                                                                          | ;OUTPUT OF 1ST SUPPORT VALUE TO PHREG. 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|                          | MOV<br>MOVX<br>DEC<br>INC                                                                                                           | A,R4<br>A,@A+DPTR<br>@R0,A<br>R0<br>R4                                                                  | ;OUTPUT OF 2ND SUPPORT VALUE TO PHREG. 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|                          | MOV<br>MOVC<br>MOVX<br>SJMP<br>END                                                                                                  | A,R4<br>A,@A+DPTR<br>@R0,A<br>ABFR                                                                      | OUTPUT OF 3RD SUPPORT VALUE TO PHREG. 1<br>QUERY NUMBER OF STEPS                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|                          |                                                                                                                                     |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

#### To Listing 2:

Definition of the registers and flags listed in the output routine:

R0 = Address counter for phase registers 1, 2 and 3 R1 = Latch for starting address of table (high byte) = Latch for starting address of table R2 (low byte) R4 = Index counter for addressing the respective table value = Counter for determining pulses/steps R7 10H = Reload register for R7 = Contains actual number of table values 11H 12H = Latch for 10 H after switch evaluation 13H = Latch for 11 H = Latch for TH0 | and value assignment 14H TH0 = Reload register for timer 0 in auto reload mode bit 32.0 = Direction flag bit 32.2 = Transfer flag bit 32.3 = Debounce flag (for switch query) bit 32.5 = Flag for changing direction bit IE.7 = Inhibit flag for all interrupts

#### Siemens Worldwide

#### Federal Republic of Germany and Berlin (West)

Salzufer 6-8 1000 Berlin 10 ② (030) 3939-1, IX 1810-278 FAX (030) 3939-2630 Ttx 308190 — sieznb

Contrescarpe 72 Postfach 107827 2800 Bremen

② (0421) 364-0, □x 245451

FAX (0421) 364-2687

Siemens AG Lahnweg 10 Postfach 1115 4000 Düsseldorf 1 **②** (0211) 399-0, T⊠ 8581301 FAX (0211) 399-2506

Siemens AG Rödelheimer Landstraße 5-9

6000 Frankfurt 1 **☎** (069) 797-0, **፲**፪ 414131-0 FAX (069) 797-2253

Siemens AG Lindenplatz 2 Postfach 105609 2000 Hamburg 1

② (040) 282-1, ☑ 215584-0 FAX (040) 282-2210

Siemens AG Am Maschpark 1

Switzerland

Postfach

Findikli

Istanbul

Siemens-Albis AG

Freilagerstraße 28

CH-8047 Zürich

P.K. 1001 Karakoey

Postfach 5329 3000 Hannover 1 ② (0511) 129-0, I

✓ 922333 FAX (0511) 129-2799

ETMAŞ Elektrik Tesisati ve

**☎** (01) 1452090, **፲**፮ 24233

Siemens AG Richard-Strauss-Straße 76 Postfach 202109 8000 München

② (089) 9221-0, ™ 529421-01

FAX (089) 9221-4499

Siemens AG Von-der-Tann-Straße 30 Postfach 4844 8500 Nürnberg 1

**☎** (0911) 654-0, 🖾 622251 FAX (0911) 654-4064

Siemens AG Geschwister-Scholl-Straße 24 Postfach 120 **7000 Stuttgart 1 ☎** (0711) 2076-0, **፲**፰ 723941-0

FAX (0711) 2076-3706

#### Europe

Siemens AG

Austria Siemens Aktiengesellschaft

Österreich Postfach 326 -1031 Wien

**☎** (0222) 7293-0, **፲**፯ 1372-0

**Belaium**

Siemens S.A. chaussée de Charleroi 116 B-1060 Bruxelles

Denmark

Siemens A/S Borupvang 3 DK-2750 Ballerup **☎** (02) 656565, **™** 35313

Finland

Siemens Osakeyhtiö PI 8 SF-00101 Helsinki 10

France

Siemens S.A. BP 109 F-93203 Saint-Denis CEDEX 1 ☆ (1) 48206120, Tx 620853

Great Britain

Siemens Ltd. Siemens House Windmill Road Sunbury-on-Thames Middlesex TW 16 7HS

Greece Siemens AE

Voulis 7 -P.O.B. 3601 GR-10247 Athen  Ireland

Siemens Ltd. Unit 8-11 Slaney Road Dublin Industrial Estate Finglas Road Dublin 11 **☎** (01) 302855, **፲** 24129

Itaiy

Siemens Elettra S.p.A. Via Fabio Filzi, 29 Casella Postale 10388 I-20100 Milano

(02) 67661, T⊠ 330261

Netherlands

Siemens Nederland N.V. Postb. 16068 NL-2500 BB Den Haag ☎ (070) 782782, ፲☑ 31373

Norway Siemens A/S Østre Aker vei 90 Postboks 10, Veitvet N-0518 Oslo 5 **☎** (02) 153090, **፲** 18477

Siemens S A R L Avenida Almirante Reis, 65 Apartado 1380 P-1100 Lisboa-1

Spain

Siemens S.A. Orense, 2 Apartado 155 E-28080 Madrid

**☎** (01) 4552500, **☎** 27247

Sweden Siemens AB Hälsingegatan 40 Box 23141

S-10435 Stockholm  **Africa** South African Republic

Siemens Limited Siemens House, PO.B. 4583 2000 Johannesburg **☎** (011) 7159111, 🖼 4-22524

America

Argentina

Siemens S.A. Avenida Pte. Julio A. Roca 516 Casilla Correo Central 1232 RA-1000 Buenos Aires ☆ (01) 300411,

☑ 21812

Brazil

Siemens S.A. Sede Central Caixa Postal 1375. 01051 São Paulo-SP (011) 833-2211 11-23641

Canada

Siemens Electric Limited 7300 Trans-Canada Highway P.O.B. 7300, Pointe Claire, Québec H9R 4R6 **☎** (514) 6957300 TX 05-822778

U.S.A.

Mühendislik A.Ş. Meclisi Mebusan Caddesi 55/35 Power semiconductors: Siemens Components, Inc Colorado Components Division 800 Hoyt Street Broomfield, Colorado 80020 (303) 469-2161 Ix 454357 sie colo

> Optoelectronic semiconductors: Siemens Components, Inc. Optoelectronics Division 19000 Homestead Road Cupertino, California 95014

TX 352084 sie lit opto

All other products: Siemens Components, Inc. Special Products Division 186 Wood Avenue South Iselin, New Jersey 08830 (201) 321-3400 Tx 844491 sie isln a

Siemens India Ltd. Head Office 134-A, Dr. Annie Besant Road, Worli P.O.B. 6597 Bombay 400018 4938786, IX 75142

Japan

Fuji Electronic Components Ltd. New Yurakucho Bldg., 8F 12-1 Yurakucho 1-Chome. Chiyoda-ku Tokyo 100 (03) 201-2401, ™ 32182

Siemens Flectrical Engineering Co., Ltd. C.P.O.B. 3001 Seoul

Singapore

Siemens Components Pte. Ltd. Promotion Office 10-15 E, 5th floor 47 Ayer Rajah Crescent No. 06-12 Singapore 0513

☎ 776'0044, TX RS 21000

Taiwan

TAI Engineering Co. Ltd. 6th Floor Central Building 108, Chung Shan N. Rd. Sec. 2 P.O.Box 68-1882 Taipei

**☎** 5363171, **☎** 27860

#### Asia

Hongkong

Jebsen & Co., Ltd. Siemens Division Honakona **☎**(05) 8233777, ፲፯ 73221 Australia

Siemens Ltd. 544 Church Street, Richmond Melbourne, Vic. 3121

Straightforward ordering with the catalog "Siemens Components Service, Preferred Products".

Every year, a revised edition of the SCS catalog on Preferred Products is published. This catalog comprises preferred products of the entire Siemens components program including their main technical specs.

Orders for components as well as for the above mentioned catalog should be directed to your nearest Siemens Office, Components Division, or Distributor.

Published by Siemens AG, Bereich Bauelemente, Vertrieb, Produktinformation, Balanstraße 73, D-8000 München 80

For the circuits, descriptions, and tables indicated no responsibility is assumed as far as patents or other rights of third parties are concerned. The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Offices of Siemens Aktiengesellschaft in the Federal Republic of Germany and Berlin (West) or the Siemens Companies and Representatives Worldwide.

S7 e 7/86 a