MIKROCOMPUTER-SYSTEME

**SMS**

**SPRINT**<sup>TM</sup>

The Universal Programmer

for your Personal Computer

**OPERATION MANUAL**

**October 1989**

(Updated February 1990)

**SPRINT EXPERT** and **SPRINT<sup>plus</sup>** are registered trademarks.

**SPRINT<sup>plus</sup>** (tm), **SPRINT EXPERT** (tm)

Software and Manuals Copyright (c) 1985 to 1989

by Programmable Device Consultants Ltd;

**SPRINT<sup>plus</sup>** (tm) **SPRINT Expert** (tm)

Hardware Copyright (c) 1985 to 1989

by SMS Microcomputer Systems GmbH;

Im Morgenland 13

8994 Hergatz-Schwarzenberg

West Germany

Telephone (49) 07522 5018

Fax (49) 07522 8929

PAL (tm) is a registered trademark of Advanced Micro Devices Inc.

## **CONDITIONS OF SALE**

SMS GmbH and PDC Ltd grant to the purchaser a single user, non-transferable, non-exclusive license for the use of this **SPRINT** software and hardware. The licensee may not transfer, assign or sub-license either the software, manuals or hardware of **SPRINT**. This license is granted on an 'AS IS' basis. Neither SMS GmbH nor PDC Ltd make any warranties, either express or implied, regarding the application or operation of **SPRINT**. Under no condition will either SMS GmbH or PDC Ltd be held liable for any direct, indirect, special or consequential damages caused or alleged to be caused directly or indirectly by **SPRINT**, including but not limited to loss of business, anticipation of profits, interruption of services, injury or physical damage. The liability for all effects of devices programmed by **SPRINT** rests completely with the licensee. Any disputes will be settled by the courts of West Germany.

## TABLE OF CONTENTS

### i. INTRODUCTION

|                                   |     |

|-----------------------------------|-----|

| SPRINT OVERVIEW                   | i.1 |

| SPRINT SYSTEM COMPONENTS          | i.2 |

| STARTING SPRINT                   | i.4 |

| DEFAULT PATHS AND FILE EXTENSIONS | i.6 |

| 'MORE' (SCREEN PROMPT)            | i.7 |

| BATCH MODE OPERATION              | i.7 |

| FILE INPUT MODE                   | i.8 |

| DEVICE REVERSAL AND CONTINUITY    | i.9 |

| I/O ADDRESSING CONFLICTS          | i.9 |

### 1. SPRINT PROM FUNCTIONS

|                                  |      |

|----------------------------------|------|

| STARTING PROM                    | 1.1  |

| AUTOMATIC DEVICE SELECTION       | 1.2  |

| BUILT-IN 'WALL CHART'            | 1.2  |

| FAMILY AND DEVICE SELECTION      | 1.3  |

| MAIN MENU                        | 1.4  |

| COMMAND LINE OPTIONS             | 1.4  |

| PROM PROGRAMMING COMMANDS        | 1.5  |

| A. SET ADDRESSING RANGE          | 1.5  |

| B. BLANK CHECK                   | 1.5  |

| C. CHANGE DEVICE TYPE            | 1.6  |

| D. DOS COMMANDS                  | 1.6  |

| E. EDIT MEMORY CONTENTS          | 1.7  |

| F. FILL MEMORY                   | 1.8  |

| H. HANDLER INTERFACE             | 1.8  |

| I. INPUT DATA INTO MEMORY        | 1.8  |

| L. LIST MEMORY CONTENTS          | 1.10 |

| M. MANUAL PRODUCTION PROGRAMMING | 1.17 |

| O. DISPLAY OPTIONS               | 1.11 |

| P. PROGRAM DEVICE                | 1.12 |

| Q. QUIT                          | 1.13 |

| R. READ DEVICE TO MEMORY         | 1.13 |

| T. GANG/SET OPTIONS              | 1.17 |

| V. VERIFY DEVICE                 | 1.14 |

| W. WRITE BUFFER DATA TO DISK     | 1.14 |

| PROM ERROR MESSAGES              | 1.15 |

| PROM NOTES                       | 1.16 |

## 2. SPRINT PLD FUNCTIONS

|                                  |      |

|----------------------------------|------|

| STARTING PLD                     | 2.1  |

| MAIN MENU                        | 2.3  |

| MORE ? ERROR DISPLAY             | 2.3  |

| PLD PROGRAMMING COMMANDS         | 2.4  |

| A. ASSEMBLE                      | 2.4  |

| B. BLANK CHECK                   | 2.4  |

| C. CHANGE DEVICE TYPE            | 2.5  |

| CROSS PROGRAMMING                | 2.6  |

| D. DOS COMMANDS                  | 2.6  |

| E. EDIT MEMORY CONTENTS          | 2.7  |

| G. EXERCISE DEVICE               |      |

| (EDIT TEST VECTORS               | 2.9  |

| STARTING EXERCISOR               | 2.10 |

| JEDEC LEVELS                     | 2.12 |

| MANUALLY SETTING LEVELS          | 2.13 |

| VCC DRIVERS                      | 2.14 |

| FUNCTIONS                        | 2.14 |

| EXECUTION SPEED CONSIDERATIONS   | 2.16 |

| H. HANDLER INTERFACE             | 2.17 |

| I. INPUT DISK DATA INTO MEMORY   | 2.17 |

| L. LIST MEMORY CONTENTS          | 2.18 |

| M. MANUAL PRODUCTION PROGRAMMING | 2.18 |

| O. DISPLAY OPTIONAL INFORMATION  | 2.19 |

| P. PROGRAM DEVICE                | 2.20 |

| Q. QUIT                          | 2.21 |

| R. READ DEVICE TO MEMORY         | 2.21 |

| S. SET SECURITY PROTECTION FUSE  | 2.22 |

| T. TEST PLD USING TEST VECTORS   | 2.23 |

| SOURCES OF TEST VECTOR ERRORS    | 2.25 |

| U. UN-ASSEMBLE DEVICE            | 2.27 |

| V. VERIFY DEVICE                 | 2.27 |

| W. WRITE BUFFER DATA TO DISK     | 2.27 |

| X. TRANSLATE JEDEC MAP           | 2.28 |

| PLD ERROR MESSAGES               | 2.29 |

| JEDEC FILE STANDARD              | 2.31 |

### 3. SOCKET PODS AND ADAPTERS

|                                                            |      |

|------------------------------------------------------------|------|

| <b>1. SPRINT EXPERT TOP PODS</b>                           | 3.1  |

| EXCHANGING THE TOP UNIT                                    | 3.1  |

| TOP 40 DIP                                                 | 3.2  |

| TOP 432 DIP                                                | 3.4  |

| TOP 432 GANG PROGRAMMING                                   | 3.5  |

| TOP 432 SET PROGRAMMING                                    | 3.5  |

| TOP 3 PLCC (20, 28 AND 32 PINS)                            | 3.7  |

| TOP 44 PLCC, LCC, PGA                                      | 3.8  |

| TOP 68 PLCC, LCC, PGA                                      | 3.10 |

| <b>2. SPRINT<sup>plus</sup> PODS</b>                       | 3.12 |

| EXCHANGING THE POD                                         | 3.12 |

| FILTER SWITCHES                                            | 3.13 |

| 28 PIN UNIVERSAL DIP                                       | 3.14 |

| 32 PIN MEGABIT EPROM POD                                   | 3.15 |

| 40 PIN MEGABIT EPROM POD                                   | 3.15 |

| 8751 MICROCONTROLLERS: POD51 AND                           |      |

| ADAPTER S422                                               | 3.16 |

| SPRINT <sup>plus</sup> DIP ADAPTERS                        | 3.16 |

| <b>3. SPRINT EXPERT AND SPRINT<sup>plus</sup> ADAPTERS</b> | 3.17 |

| GENERAL PURPOSE SMD ADAPTERS                               | 3.18 |

| SPECIAL PURPOSE DIP ADAPTERS                               | 3.19 |

| <b>4. SPRINT EXPERT MULTI-SITE SYSTEMS</b>                 | 3.20 |

| DUAL CONFIGURATIONS                                        | 3.20 |

| QUAD CONFIGURATIONS                                        | 3.20 |

| OCTAL CONFIGURATIONS                                       | 3.20 |

| HEX CONFIGURATIONS                                         | 3.20 |

## 4. PLDASM

|                                   |      |

|-----------------------------------|------|

| PROGRAMMABLE LOGIC DEVICES        | 4.1  |

| BOOLEAN FUNCTIONS                 | 4.2  |

| BOOLEAN TO JEDEC TRANSLATION      | 4.4  |

| <b>SPRINT PLD MACRO ASSEMBLER</b> | 4.5  |

| COMMAND LINE OPTIONS              | 4.6  |

| PLDASM SYNTAX                     | 4.7  |

| COMMENTS                          | 4.7  |

| LABEL DEFINITION                  | 4.7  |

| DEVICE DEFINITION                 | 4.8  |

| SECURITY FUSE CONTROL             | 4.8  |

| PIN DEFINITION                    | 4.9  |

| MACRO DEFINITION                  | 4.10 |

| <br>EQUATIONS                     | 4.11 |

| FUNCTIONS                         | 4.12 |

| INTERNAL NODES                    | 4.13 |

| ACTUAL BOOLEAN EQUATIONS          | 4.14 |

| CLOCKS                            | 4.14 |

| OUTPUT ENABLE                     | 4.15 |

| CLOCKS, XOR, SPECIAL FEATURES     | 4.16 |

| FUSE                              | 4.18 |

| VECTORS                           | 4.18 |

| END OF FILE                       | 4.18 |

| RESERVED WORDS                    | 4.19 |

| SPRINT PLDASM EXAMPLE             | 4.20 |

| EXAMPLE JEDEC FILE                | 4.22 |

| SPRINT PLDASM OPERATION           | 4.23 |

| SPRINT PLDASM ERROR MESSAGES      | 4.24 |

| APPLICATION NOTE                  | 4.26 |

| PROGRAMMABLE FEEDBACK OPTIONS     | 4.27 |

| HIDDEN (BURIED) REGISTERS         | 4.27 |

| DUAL FEEDBACKS                    | 4.28 |

| PLX TECHNOLOGY PLX448/464         | 4.31 |

| INTERNAL NODE NUMBERING           | 4.32 |

| DEVICE NAMES AND FEATURES         | 4.33 |

| EP600, EP900 JK AND RS FLIP FLOPS | 4.36 |

| USE OF T TYPE FLIP FLOPS          | 4.36 |

## 5. SPRINT UN-ASSEMBLER OPERATION

|                              |     |

|------------------------------|-----|

| UN-ASSEMBLER UTILITY - UNASM | 5.1 |

| PAL EMULATION - TRANSLATION  | 5.1 |

| STARTING UNASM               | 5.2 |

| COMMAND LINE OPTIONS         | 5.2 |

| DEVICE LIST                  | 5.2 |

| USER PIN NAMES               | 5.3 |

| UNASM OPERATION              | 5.3 |

## APPENDICES

### A. TECHNICAL NOTES

|                                              |     |

|----------------------------------------------|-----|

| SPRINT <sup>plus</sup> TECHNICAL DESCRIPTION | A.1 |

| SPRINT EXPERT TECHNICAL DESCRIPTION          | A.3 |

### B. INSTALLATION

|                                                              |     |

|--------------------------------------------------------------|-----|

| HARDWARE INSTALLATION                                        | B.1 |

| CHANGING SPRINT <sup>plus</sup> I/O PORT ADDRESSES           | B.2 |

| CHANGING SPRINT EXPERT HW I/O PORTS                          | B.3 |

| SOFTWARE INSTALLATION                                        | B.4 |

| SPRINT EXPERT INITIAL SYSTEM CHECKOUT<br>WITH TESTEX         | B.7 |

| SPRINT <sup>plus</sup> INITIAL SYSTEM CHECKOUT WITH<br>TEST2 | B.7 |

| SPRINT EXPERT CALIBRATION UTILITY                            | B.8 |

| SPRINT <sup>plus</sup> CALIBRATION UTILITY                   | B.9 |

### C. USER DOCUMENTATION

|                    |

|--------------------|

| UPDATE CERTIFICATE |

| WARRANTY           |

## INTRODUCTION

### SPRINT OVERVIEW

Congratulations on purchasing this **SPRINT** programming tool. You will now experience the ease of use and flexibility that has made the **SPRINT** family the leading 'personal programmer' for professional users. With the **SPRINT** family, we have achieved professional quality combined with user upgradability at an affordable price. Our **SPRINT<sup>plus</sup>** system is the original design, with a 28 pin socket for most devices, and optional 32 and 40 pin sockets for higher density circuits. **SPRINT EXPERT** is our newest system with a 40 pin socket, and exchangeable socket concept for higher pincount and SMD devices. Both **SPRINT** systems support PLCC, SOIC and LCC devices via industry standard adapters.

**SPRINT** is a convenient programming tool for all kinds of programmable devices, including PROMs and EPROMs (Erasable Programmable Read Only Memories), Flash EPROMs, EEPROMs (Electrically Erasable Programmable Read Only Memories), PALs (Programmable Array Logic), EPLDs (Erasable Programmable Logic Devices), Microcontrollers, and more. All popular technologies can be programmed, including bipolar, NMOS, CMOS, ECL, and even GaAs. **SPRINT** uses the popular IBM and IBM-compatible desktop computers as its 'host' system for data and algorithm storage, while actual programming is under control of the hardware pulse generators and D/A converters of the **SPRINT** system. **SPRINT** is very user-friendly, no special knowledge of programmable devices is required. All operations are menu driven and displayed in clear, easy to understand English text. In addition to the programming ability of **SPRINT**, we have added dozens of additional software features, including a Macro assembler for PLDs and EPLDs, an un-assembler, vector test support with vector editor, EPROM editors, multiple disk I/O modes and more.

One key advantage of **SPRINT** is the ability to add new devices and features without modifying the hardware. Software updates are released on floppy disk three times each year. Each system sold can be updated for 6 months after the date of purchase with new devices and features at no cost. After 6 months, the **SPRINT** Software Maintenance Plan (SMP) automatically distributes 3 updates each year to the user.

We are responsive to your needs. Please write to us if you would like to have any devices added to the list of presently supported chips. We add devices as soon as they become available to us, with the priority set by feedback from our many customers.

Because the list of supported devices is growing rapidly, this Manual contains no device list. All selections are menu driven with vendor names and part numbers. You may create your own list from the device menu onto the printer with the '\*\*' key, or to a disk file with the '+' key.

## SPRINT SYSTEM COMPONENTS

The **SPRINT** package consists of three basic functional units:

### 1) An IBM Compatible Plug-in Board

The **SPRINT** plug-in board contains all the hardware logic that is required to interface between the IBM compatible PC/XT/AT computer and the device socket. The **SPRINT** board produces all the necessary voltages that are required to program the supported logic devices.

The **SPRINT** board should be left permanently installed in the user's IBM compatible PC/XT/AT computer, it does not interfere with normal operation. Chapter 5 describes the installation of **SPRINT** in any IBM PC/XT/AT or compatible computer.

### 2) Floppy Disk Based Software

The standard **SPRINT** package contains two floppy disks with the programs and utilities that enable you to use **SPRINT**. The programs are all menu driven and easy to use. The programs on the floppy disk directly control the hardware logic on the **SPRINT** plug-in board and socket pod to produce the correct programming voltages for the selected device. The list of devices supported by **SPRINT** is continually being updated, a printer list is quickly out of date. A full list of devices supported by your software version may be obtained from within the programming utilities. Please turn to Sections 1 and 2 of this Manual for more details.

**3) An External Device Socket Unit (POD) With a Zero-Insertion Force Dual Width Socket.**

**a) SPRINT EXPERT**

The **SPRINT EXPERT** external hardware consists of two parts. The bottom unit (POD BASE) contains the actual pin driver logic, this keeps the signal length to a minimum and allows 100% SW programmable pins. The socket is located in the upper unit (POD TOP) and is exchangeable for other types of sockets. Examples of TOPs include

- a) 40 pin DIP socket,

- b) 4 x 32 pin DIP E/E/PROM gang/set module,

- c) 20/28/32 pin PLCC/LCC module,

- d) 44 pin PLCC/LCC socket,

- e) 68 pin PLCC/LCC socket,

- f) various PGA sockets

Other modules will also be available. The base is connected to the IBM type plug-in board via the '**SPRINTbus**'. The cable length of 90 cm allows the computer to be on the floor or otherwise located a distance away from the programming socket. All pinouts are selected by relays inside of the POD.

**b) SPRINT<sup>plus</sup>**

**SPRINT<sup>plus</sup>** uses a 28 pin external socket in a small box located outside of the computer. It is connected to the computer by a flat ribbon cable.

Attention! This cable must not be made longer or errors will occur.

The socket is used by **SPRINT** to provide the connection to the programmable device. This box is called the 'POD'. The standard POD supports devices in DIP packages with up to 28 pins. Other PODs support 32 and 40 pin EPROMs. In addition, various socket adaptors are available, supporting a variety of special devices and packages that do not fit into the 28 pin DIP socket. PODs for 32 and 40 pin devices as well as adapters for Lcc and PLcc circuits are also available.

**NOTE:** Before reading or programming any device with **SPRINT<sup>plus</sup>**, be sure to set the 'Filter' switches on the socket pod to match the diagram shown on the screen. If **SPRINT<sup>plus</sup>** can detect an incorrect filter setting, prompt the user to correct the setting. In any case, failure to set the switches correctly may result in damaged devices.

## STARTING SPRINT

The user should follow the instructions detailed in the Installation Section of this Manual in order to ensure correct installation (and eventual calibration) of the **SPRINT** Programming Module.

With the **SPRINT** board installed according to the installation instructions, power-on your computer. If using a hard disk, select the **SPRINT** directory. If using a floppy based system, insert your copy of the **SPRINT PROM** disk into the floppy disk drive. Enter the command:

**A>SPRINT<cr>**

The **SPRINT** master menu as shown below will appear.

|   |   |                                   |

|---|---|-----------------------------------|

| 1 | = | Logic devices (PAL, EPLD, etc)    |

| 2 | = | Memory devices (PROM, EPROM, etc) |

| 3 | = | PLD Assembler                     |

| 4 | = | PLD Un-Assembler                  |

| 5 | = | TEST Utility                      |

| Q | = | Exit                              |

Enter Selection

You may now select the program you wish to run. Enter a '1' for PALs, and EPLDs. Enter a '2' for EEPROMs, EPROMs, PROMs and microcontrollers. You may also start the programs without the master menu by typing 'PAL', 'PROM', 'PLDASM', 'UNASM', or 'TEST' directly at the MSDOS prompt, e.g.:

**A>PROM<cr>**

This will immediately start the EPROM programming utility without the need for entering the main menu.

Sections 1 through 4 of this Manual describe the use of these specific programming utilities in detail. All the utilities are menu driven. The user is prompted with clear instructions for action. All keys typed by the user may be in upper or lower case letters.

The Manual is divided into sections on the utilities supplied with **SPRINT**.

- For EPROMs, EEPROMs, PROMs, microcontrollers, and other memory devices, the 'PROM' program should be used as described in Chapter 1.

- For programmable logic devices: 'PLDs', 'EPLDs', and 'PALS', the 'PAL' program should be used as described in Chapter 2.

- All special adapters, including instructions for **SPRINT EXPERT** with the TOP432 unit, and **SPRINTplus** with 32 and 40 pin EPROMs (MEGA32 and MEGA40 adapters) are described in Chapter 3.

- The PLDASM utility is provided as a tool for creating JEDEC files from Boolean equations for the 'PAL' utility; details on the operation of the **SPRINT PLDASM Macro Assembler** may be found in Chapter 4.

- The PLD Un-Assembler is described in Chapter 5.

- For periodic checkout and calibration of the hardware components of **SPRINT**, the program 'TEST' is provided (see Installation Section, Appendix B of this Manual for details).

## DEFAULT PATH AND FILE EXTENSIONS

The default path for all of **SPRINT** software is the path from which the program was called. This path will be used to display the directory when inputting data. The default extension (file type) depends on the program called; the defaults are:

| <u>Program</u> | <u>Default Extension</u> |

|----------------|--------------------------|

| PLDASM         | .PLD                     |

| PROM           | .COM                     |

| PAL            | .JED                     |

| UNASM          | .JED                     |

The default file extension and the default path may be changed by entering the desired default when starting **SPRINT**. The software will extract the path and file type from the sample file description on the command line. For example :

PROM \hexdata\\*.hex

will change the default to all files with the file extension '.hex' in the subdirectory 'hexdata'. In this manner, another program (like ISDATA LOG/iC) can start one of the **SPRINT** programs with any directory or file type being used initially during the Input data command.

If **SPRINT** has been executed previously, a file with the extension '\$\$\$\$\_.CNF' will have been created or updated in the current directory. This file contains the drive, directory and file extension parameters, the file name, as well as other user options, that were set up by the user in the previous session. This simplifies the use of **SPRINT** in development environments by maintaining an automatic setup state each time the software is started. For best use of this feature, place **SPRINT** files in a directory '/SPRINT' and add '/SPRINT' to your PATH command.

The .CNF files that are created by the different utilities are:

|                 |                                    |

|-----------------|------------------------------------|

| JED\$\$\$\$.CNF | For the PLD programming utility    |

| COM\$\$\$\$.CNF | For the PROM programming utilities |

| PLD\$\$\$\$.CNF | For the PLD assembler              |

Please refer to the Input Command Function in this Manual for more details.

## SCROLL CONTROL - MORE ?

All commands support controlled scrolling of the screen. When **SPRINT** has filled a screen with data, the question 'More?' is displayed. Answering '.' or 'n' will terminate the command, any other key will allow an additional 20 lines of text to be displayed.

## BATCH MODE

Operating **SPRINT** from a batch file allows many special, customer defined applications. For example, a serial number could be entered into the memory buffer to allow EPROMs to be serially numbered. A user could embed **SPRINT** into a completely different application using the batch mode. In effect, all keystrokes from the keyboard can be replaced by a file on the disk. For our examples we will call this file 'FILEB'. With the batch mode a device can be selected, a file read-in, and a device programmed - all automatically. All **SPRINT** programming modules support batch mode. For example, with PROM, batch mode is selected by starting PROM as shown below:

```

> PROM -bFILEB

```

'FILEB' ends either when no more data is in the file, or when a 'Q' character is read while in the main menu. It is also possible to start the **SPRINT** drivers with a default batch file. If a file JED\$\$\$\$.CNB or COM\$\$\$\$.CNB is found on the disk when starting PAL or PROM, then this file will be read as a batch file. The user can use any editor to create this file. Note that the ^J key (0x0A) is the same as the cursor key. Function keys F1 to F9 are represented as ~1 to ~9.

EXAMPLE BATCH FILE : blank check Xilinx 1736:

```

~8abq

```

If any error occurs during batch mode, a 'N' is given as the response any internal error control questions, for example 'skip blank check [N]' will have a N response in batch mode. When the **SPRINT** software exits to the calling program, there will be an return code with the following values:

|        |                                                   |

|--------|---------------------------------------------------|

| 0      | no error, normal termination                      |

| 1      | general error (not blank, programming fail, etc)  |

| 2      | batch file error (not found etc)                  |

| 3      | Device reversed or pin continuity error           |

| 0x20-F | (TOP432 only) indicates which EPROM socket failed |

## FILE INPUT MODE

All SPRINT programs use the same file input format. When a file is to be read, the system will display on the screen, the files in the default directory with the default extension (see defaults above). The highlight bar may be positioned to any entry on the screen by using the cursor keys. An entry is selected by typing <return>.

The input screen shows the current drive, current directory, file type option, and those files that match the type selected. Actual files are displayed with an extension (in yellow color on a color monitor). Selecting a file will take the user to the next menu. Other entries on the screen with non-matching extensions are directories (purple on a color monitor). The entry '..' refers to the root directory; selecting that entry will change the current directory to the root directory. Choosing any other directory entry will select the chosen directory for display.

It is also possible to directly type in any file name instead of using the cursor keys (useful in batch mode). The file extension must be entered, followed by a return. For example, a 2764 binary file on the root directory of drive b could be:

B:\T2764.COM

**NOTE:** When the default drive, directory or file extension is modified in the input command, the new default values are stored in a configuration file (\$\$\$\$.CNF). This configuration file is read (if it exists on the disk in the current default directory) to determine the default parameters that were used in the previous session of the PROM utility, the Input command will use these same parameters as default in the current session by referencing the configuration file.

## DEVICE REVERSAL AND CONTINUITY TESTING

**SPRINT EXPERT** includes the additional feature of device socket testing. Before any operation that applies voltage to a device is started, the connection of the device to the socket is first tested. A backwards or offset device will cause an error message, as will a device with a bent pin. A device with more pins than expected will also cause an error. The operator can correct the error and try again. Note that certain devices do not permit reversal and pin testing.

Should **SPRINT EXPERT** report a pin continuity error, the user will have the option to abort the operation with <ESC> or to retry the operation with 'Y', or to ignore the message and proceed with '#'. We strongly recommend not to continue if this error message occurs.

## I/O ADDRESSING CONFLICTS

If for any reason **SPRINT** does not operate correctly in the system, please check first if another board in the system is using the same address as the **SPRINT** card. See the installation section for information on the default port addresses, and how to change them.

## 1. SPRINT PROM FUNCTIONS

### STARTING PROM

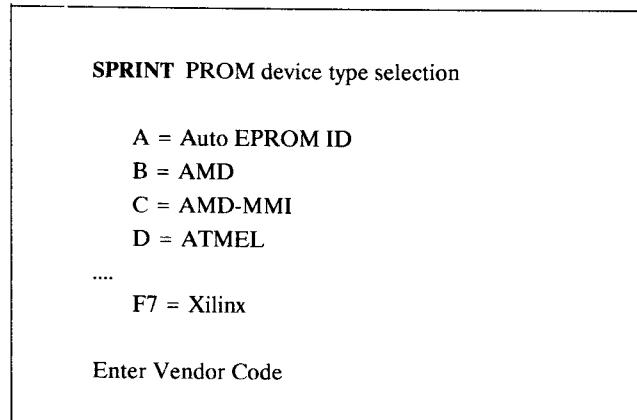

The **SPRINT PROM** software controls the **SPRINT** hardware in order to program data into PROM based devices. Start PROM either from the main **SPRINT** menu, or directly from DOS. A menu of PROM manufacturers and vendors will appear on the screen. Next to each vendor in the menu is a single letter or function key vendor code as shown below:

The user is then prompted for the key code of vendor of the device that is to be programmed. At this point, the user should type the single key corresponding to the vendor of the device to be programmed. For example, entering a 'D' following this prompt would select Atmel, 'F7' would select Xilinx, etc. The **<Esc>** key returns operation to the main menu.

## AUTOMATIC DEVICE SELECTION

In order to auto-configure the PROM programming utility to match the EPROM currently inserted in the socket, the user may optionally type an 'A'. This will cause the PROM utility to attempt to read the device in the socket using 'silicon signature', determine its type and to configure itself for that device. If any error occurs in attempting to read the device in the socket, due to no device in the socket or a device which does not support silicon signature, no auto-configuring will take place. Note - silicon signature must only be used with EPROMs, and: some EPROM vendors have used the same ID codes. Always confirm the Auto ID selection.

**SPRINT EXPERT** automatically determines the number of pins in the device and applies the correct Vcc, Gnd and selection voltages.

**SPRINTplus**, 28 pin POD, should have switches 1 and 2 off during selection. Mega32 switch 1 should be on for 28 pin devices, and off for 32 pin devices. Check the filter switch settings after selection is complete.

## BUILT-IN 'WALL CHART'

The user may optionally make a printout of all the PROM and EPROM devices supported by the version of the PROM utility that is being used. This is done by typing a '\*\*' instead of the vendor code. If the printout should go to the disk instead of the printer, the '+' key can be pressed.

During printing of a device list, the option exists to use the 132 column mode of the printer. This function works with IBM compatible (or EPSON type) printers only. The 132 column mode can optionally be turned off at the end of the print cycle as well. The printout will show the complete list of devices supported by **SPRINT**. Some devices may be marked 'requires SMP'. You can access these devices by purchasing an update from your **SPRINT** distributor.

## FAMILY AND DEVICE SELECTION

After the selection of the vendor is complete, a second menu will appear on the screen. This menu lists all the devices from the selected vendor that are currently supported by the **SPRINT** PROM programming utility. This menu also has a single key code for each device supported. The device to be programmed should be selected in the same way as the vendor was selected in the previous menu. For example, if Cypress was the selected Vendor and the device to be programmed was a CY7C291, the user would have typed 'B' for Cypress in the first menu and 'G' for CY7C291 in response to the second menu. Following is an example of a device table as it might appear on the screen

|                                        |              |

|----------------------------------------|--------------|

| PROM device table for vendor = Cypress |              |

| A = CY7C225                            | B = CY7C235  |

| C = CY7C245                            | D = CY7C251  |

| ...                                    |              |

| O = CY7C291A                           | P = CY7C293A |

| Enter Selection                        |              |

Non-supported device selections are ignored. The working size of the memory buffer is automatically set to the device size selected. The first time any device is selected, the memory buffer is initialized to the value set by the 'default buffer contents flag' (see Options). The default buffer size is 32 Kbyte; larger memory buffers are allocated to devices that require more than 32 Kbyte to store the entire device contents. Attention: if your PC does not have enough memory installed, an error message will be displayed. A checksum of the active area in the memory buffer is calculated and displayed on the main menu screen. For large devices, like the 27020, checksum calculation may take a few seconds. If the device size is larger than 2 megabits, **SPRINT** will use the disk as storage. **SPRINT** does not require any EMS or EXPANDED memory.

Some registered PROM devices have, in addition to the data array, additional reset and enable functions. **SPRINT<sup>plus</sup>** automatically adjusts the total memory size to include these extra functions. Also, for those microcontrollers that support a security fuse, an extra byte is assigned to control this function. These extra features, such as security fuses, initialize bytes, enable options etc, are always set to zero when a device is selected.

The <Esc> key will cause PROM to display the vendor selection menu again.

## MAIN MENU

Following the device selection, the main PROM programming utility menu is displayed on the screen. This menu is composed of a list of commands. Command selection is performed with a single key stroke (the letter corresponding to the command in the menu). Commands may be selected with either upper case or lower case letters: SPRINT will understand both. The function of each command is described in the following paragraphs of this chapter. In the top right-hand corner of the screen the vendor and device that have been chosen are displayed. If this is does not correspond to the vendor or the device that is to be programmed, then the user may change the device type and the vendor by executing the command 'C' (Change device type), see below.

## COMMAND LINE OPTIONS

In addition to the directory and file type option described in the introduction (Default Path and File Extensions), PROM has additional command line options :

```

> PROM [-S] [-V] [-Z] [-Bfilename] [\Path\Filetype]

```

- a) -V Enables verification of programmed devices at  $V_{cc} \pm 10\%$ . The default is verification at 5.0 V.

- b) -Z Forces the buffer memory to zero at initialization and before reading files. The default forces the buffer memory to all ones.

- c) -B Causes the contents of file 'filename' to replace all keyboard entries until end of file, quit or an error is reached.

- d) -G (EXPERT) Multi base systems (Dual, Quad etc) will be activated in GANG mode - all base units must have the same TOP, all devices in all TOPs must be the same type. Programming will program all in parallel.

- e) -L (DUAL) Force selection of the left hand POD

- f) -Sn (QUAD, OCTAL) Force selection of base position #n, 1 is right-most position, then 2, 3, 4 etc.

## PROM PROGRAMMING COMMANDS

### A SET ADDRESS RANGE

Sometimes it is necessary to program a set of bytes in a PROM without programming the entire device. The set address range command 'A' allows the user to work on and affect any portion of the entire address range of the device without influencing other areas. The user will be prompted for the start and end addresses of the range to be programmed. The PROM programming utility will check on the values entered to ensure that values entered do not correspond to an address range larger than the total address range of the device.

During blank check, program and verify, only the range selected will be addressed. The added versatility of being able to specify the start address of the device in memory to be anywhere within the full address space of the complete memory buffer allows smaller PROMs to be combined together into one larger PROM. See the 'Read' command for more details on the combine function. If a range other than that which is normal for the device is set, a box will appear on the screen to display the currently active range.

**NOTE:** The checksum display on the screen refers to the entire device, not the range selected.

### B BLANK CHECK

This command verifies that the device is empty. The device in the socket is read and the contents are compared to the expected 'erased' condition. The device type selected must match the physical device inserted in the socket. Some devices require special blank check sequences, SPRINT automatically uses these sequences if required.

If the device is not blank, the message 'PROM not blank' will be displayed. Verify or EDIT can be used to examine the contents of the PROM.

EEPROM and Flash EPROMs require no blank check before programming, they will be automatically erased as part of the programming cycle. The 'B' command for these devices is not significant.

## C CHANGE DEVICE TYPE

The active device type can be changed using this command. The user is prompted by a menu with the list of currently available vendors and devices as described in the introduction to this chapter. After selection, **SPRINT** returns to the main menu.

When the device type is changed, the active memory buffer area is automatically changed to accommodate larger or smaller devices as necessary; however, data previously stored in the memory buffer remain unchanged until either a device is read, or data is read from the disk.

Pressing the Escape key 'ESC', at any time during the change device phase will return the user to the previous menu without affecting the currently selected device.

## D DOS COMMAND

This allows MSDOS commands to be executed without leaving the **SPRINT** environment. Note that the MSDOS 'COMMAND.COM' file must be either in the **SPRINT** directory, or locatable via the DOS PATH command for this to work. If large EPROMs are selected, there may not be enough room to load the MSDOS command file. Once loaded, any normal DOS command can be entered, in the same manner as in DOS itself. For example:

DIR \*.COM

will list all the files with the extension or file type ".COM" (MSDOS binary files). **SPRINT** will remain in the DOS command mode until 'EXIT' is typed on the keyboard. On completion of the DOS command, the user is returned to the main PROM utility menu.

## E EDIT MEMORY CONTENTS

Selection of this command allows the user to examine and modify the contents of the memory buffer. This Screen oriented editor displays 256 bytes (100 HEX) from the buffer at any one time. Data may be input in HEX or ASCII format.

After typing 'E' for Edit, the user will be prompted to enter the address to be edited. The user should enter the HEX address, followed by a carriage return. The screen will then display a 256 byte page of data from the memory buffer including the selected address, the cursor will be positioned to the selected location. Cursor control keys may be used to select any address location in the memory.

The Help screen lists extra data control functions in addition to the cursor movement keys. Help is displayed with the F1 key.

In order to enter TEXT mode, the user may type the ' ' key. This allows the entry of ASCII text data directly. ESC returns from TEXT mode to HEX mode.

Data may be entered while in HEX mode by simply typing in the hex data. The ASCII equivalent will be displayed at the end of each line.

The F2 key is used to directly jump to any location in memory (GOTO). After pressing F2, the user will be prompted to enter the destination address.

The F3 key is used to copy blocks of memory. After pressing F3, the user will be prompted for the start address, number of bytes (in Hex) and destination address.

The F4 key will swap all even and odd bytes in memory.

The Insert key will enable the insert mode. Normally data entered overwrites data in memory. With insert mode enabled, all locations after the location pointed to will be copied up one byte.

The '.' key or the 'ESC' key will exit the editor, with a new checksum to be calculated, and a return to the main menu. For very large devices, this can cause some seconds of delay. The correct checksum is displayed in a box to the right of the main menu screen.

## F FILL MEMORY

A range of buffer memory can be initialized to any value with this command. After 'F' is entered, the user will be prompted for the hex start address, end address, and one byte of data. The addresses and data are separated by commas. After carriage return, the range of memory will be initialized to the value entered. Fill will always change at least one byte on execution.

## H HANDLER INTERFACE

The optional handler interface is controlled by this command. The number of devices to be programmed with the pattern in memory is entered after the prompt. Then the 'P' key is entered. **SPRINT** will cycle through the number of devices selected, counting only the good units. The **SPRINT** handler interface kit is required. **SPRINT EXPERT** is strongly recommended due to the device reversal and pin continuity features.

## I INPUT DISK DATA INTO MEMORY

Loads the data from the file selected into the memory buffer. After 'I' for Input is entered, the system will display the files in the default directory with the default extension. The default extension is '\*.COM' unless otherwise specified in the original command line or the configuration file (COM\$\$\$\$.CNF, see the section Default Path and File Extensions).

See the Introduction Section for information on the use of the **SPRINT** file input mode.

After a filename is selected, the user will be prompted to enter various options about the file. The keyboard cursor up and down keys are used to point to the option required, and the value can be typed-in. The file type, Binary or Hex may be selected (default is Binary). The byte/word extraction can be specified (default is All). The starting address of the data in the file on disk can be entered, and the starting address of the data in the buffer memory can be entered (default is the 'bottom' address defined by the 'A' address range command). A return without changing any parameters starts the load process. The 'Auto' option default for the start address allows **SPRINT** to find the most likely starting address for Intel HEX files with physical starting addresses in segments other than segment 0. Inserting a 0 in this field will force the physical address 0.

There are 9 different input options for the data:

- A All for 8 bit data

- E Even for even bytes of 16 bit data

- O Odd for odd bytes of 16 bit data

- 0 Byte 0 of 32 bit data

- 1 Byte 1 of 32 bit data

- 2 Byte 2 of 32 bit data

- 3 Byte 3 of 32 bit data

- U The last 2 bytes of 32 bit data

- L The first 2 bytes of 32 bit data

The user can select any one of these options.

Before any data is read-in, if the start address is equal to 0000, the memory buffer will be reset to either 00 or FF, depending on the buffer default option. See the 'O' command for more detail. Any extra bytes (security, initialize, reset control etc) will be set to 00. Note that these extra bytes are located after the actual memory data.

If the start address is not equal to 0000, the existing data in the memory buffer is not changed. This is done to allow a files to be merged and then be programmed into devices.

Data will then be read from the specified file using the options selected, until either the 'TOP' of the memory buffer or the end of the file is reached. The number of bytes read from the file will be displayed on the screen. After reading, a new checksum value will be calculated. For very large devices, this can cause some seconds of delay. The correct checksum is displayed on the main menu screen.

Nine different file types are supported,

a) Binary Format

If this format is selected, the data in the file will be read until either the end of file or the top of the memory buffer is reached. A non-zero start address offset in the data file on the disk may be specified, the default is zero. Finally a destination address offset for the data in the memory buffer can be selected. The default for the destination address offset is the beginning of the programming range (see Set Range command 'A').

b) HEX Space

This is a string of bytes in hex format, separated by a space character. Returns and line feeds are ignored. An example of the format is shown below, it is also on the distribution floppy disk (file "DEMO.HEX"). HEX space files are terminated by an ASCII ETX (HEX 04) character.

```

STX 12 23 34 45 56 67 78 89 90 01 12 23 34 45 56 67 78 89 12 23 34 45

56 67 78 89 90 ETX

```

c) Intel HEX, standard and extended

Tektronix HEX, standard and extended

Motorola S Record, 16, 24 and 32 address modes.

These formats are supported according to each manufacturer's definition. A start address of the data in the file may be selected. With Intel and Tektronix HEX formats, both 16 and 20 bit addresses are supported, with Motorola S Records, 16, 24 and 32 bit addresses are supported.

**SPRINT** automatically determines if the HEX file is SPACE, Intel, Tek or Motorola.

## L LIST MEMORY CONTENTS

This command displays in tabular form the contents of the memory buffer. When 'L' for List is entered, the user is prompted for the start and end addresses. A comma separates these addresses. If the user wishes the display to go to the printer, a ', \*' is typed after the end address. Memory is displayed in HEX, 16 (HEX 10) bytes per line, from the start of the address range to the end of the address range. A pause is inserted after each full screen to allow the user to examine the contents of the memory buffer. The next screen of data can be displayed by entering a 'Y' or return at the end of each page. The continuation of memory display may be terminated by typing 'N' or ' ' at the end of the currently display page. The ASCII equivalent of the HEX data is also displayed at the end of each line, for data values between 32 and 127 decimal.

## O DISPLAY PROM OPTIONS

This command will display on the screen, the programming parameters **SPRINTplus** will use based on the device selected. It can be used to compare the voltages selected by **SPRINTplus** with the voltage recommended in the data sheet of the device. Any discrepancies found in the programming voltage selection should be notified to your **SPRINTplus** supplier immediately. All other parameters displayed can be useful information about the device selected, and the operation mode of **SPRINT**. The user can change any parameter shown (at his own risk!). These parameters will not be saved once the program is exited (except screen display mode). The status displayed includes:

|                                                         |   |

|---------------------------------------------------------|---|

| Installed pod type                                      |   |

| Hardware model                                          |   |

| Device size in decimal bytes                            |   |

| Type of device                                          |   |

| Vpp voltage, modifiable in 100 mv steps                 | a |

| Vcc voltage during programming, 50 mv steps             | a |

| Vendor ID (if defined) in HEX                           |   |

| Vendor device ID (if defined)                           |   |

| Width of first programming pulse                        | a |

| Maximum number of programming attempts                  | a |

| Width of last programming pulse                         | a |

| Type of programming method                              |   |

| Number of special feature bytes                         |   |

| Vcc voltage during verify                               | t |

| Screen Display mode, use slow if your screen has 'snow' | t |

| Default buffer memory contents, 00 or FF hex            | t |

| Sound BEEP at the end of the programming operation      | t |

To modify a parameter (a), enter the new value while the cursor is on the line. To toggle a flag (t), press the 'SPACE' key. The modified parameters are only used during this session, and are not stored to the disk.

## P PROGRAM DEVICE

When 'P' for Program is entered, the device in the socket can be programmed using the data stored in the memory buffer. The device type selected by the user must match the physical device in the socket. The user is prompted to confirm the programming of the device by typing a 'Y', any other key will abort the command. This has been implemented so that accidental programming of devices may be avoided. **SPRINTplus** users should verify the Filter switch settings.

After confirmation that programming of the device is to be performed, non-erasable devices will be checked for erasure (Blank check). If the device is not empty, **SPRINT** will test if the pattern in memory can be overprogrammed on top of the existing pattern in the device. If so, the user will be prompted to 'overprogram'. Entering 'Y' will allow **SPRINT** to program on top of the existing pattern. Erasable devices will be erased automatically before programming.

Then the device will be programmed using the algorithm defined by the manufacturer. Intelligent, Flashrite, Rapid, Quickpulse, Quickpro, Page Mode and all other fast programming methods are used to keep the programming time to a minimum. The programming algorithm used is automatically determined by the vendor/device type chosen. For devices with long programming times, the number of 512 byte blocks remaining to be programmed is displayed to indicate that the programming operation is processing. This is useful in large devices not using QuickPulse type algorithms. This 'ACTIVITY' display is not shown when QuickPulse devices are programmed. When the 'ACTIVITY' display is shown, programming can be interrupted with the <ESC> key.

Extra PROM and microcontroller features like Reset, Synchronous Enable and Security Locations are automatically programmed in devices which have them; these features are controlled by extra data bytes. See the PROM notes section for specific details and examples. The extra bytes in the memory buffer may be set using the buffer edit utility (see above), and can be stored to the disk with the 'W' command.

After programming, the contents of the device will be verified against the contents of the memory buffer to confirm the successful programming of the device. Following a correct verify operation, when everything has been successfully completed, the message 'PASS' appears on the screen.

If there are any errors, they will be shown on the screen, and the blinking message 'FAIL' will appear. Otherwise the message 'PASS' will be displayed. The number of devices successfully programmed with the same contents will be displayed in a box to the right of the PASS/FAIL box.

## Q QUIT

Returns the user to the **SPRINT** menu or the operating system if the menu program **SPRINT** was not used.

## READ DEVICE TO MEMORY

This command reads the contents of the device in the socket pod into the memory buffer. Note that after data has been read into memory, the same size or smaller device type may be selected without altering any data stored.

When registered PROMs are selected, the Reset Byte and Programmable Synchronous Enables (if any) are automatically read into the buffer memory for correct duplication or storage.

After reading in the data, a new checksum value will be calculated. For very large devices, this can cause some seconds of delay. The correct checksum is displayed on the main menu screen.

With the 'A' command ( = set address range), an address range larger than the physical device may be defined. This allows the user to read in several small EPROMs, at successively higher contiguous memory addresses in the memory buffer. This feature enables the user to combine the data contained in a number of small EPROMs and to program this data into one larger EPROM. The editing buffer size must be initialized first by selecting the larger device, then the smaller one. The EPROM in the socket can be read into any portion of this editing buffer. When a larger device is selected with the Change command, this editing buffer is not cleared.

Example: To combine the contents of four 2764's and to program this data into a single 27256 the following procedure may be performed.

- a) Select the vendor and device for the 2764 devices that you wish to read.

- b) Select the address range 0 - 1fff (A command)

- c) Read in the lowest addressed 2764 (R command)

- d) Select the address range 2000 - 3fff (A command)

- e) Read in the 2764 with the next address (R command)

- f) Select the address range 4000 - 5fff (A command)

- g) Read in the 2764 with the next address (R command)

- h) Select the address range 6000 - 7fff (A command)

- i) Read in the highest addressed 2764 (R command)

- j) Change the device type to 27256 (C command)

- k) Insert the 27256 device into the socket and program it (P command)

## **V VERIFY DEVICE**

Compares the contents of the device in the socket to the data in memory buffer. Any differences are displayed in clear text, with memory data, device data and address. All features of the device are verified, including extra reset and enable bits and architecture bits.

Verify may be done at nominal Vcc, or  $V_{cc} \pm 10\%$ . See command line options or the 'O' command for this feature.

## **W WRITE BUFFER DATA TO DISK**

Writes the data in the memory buffer onto the disk using the filename supplied. After entering 'W', the user will be prompted to enter a MSDOS style path. A drive label or path may optionally be entered. The default path is accepted if <Return> is entered without any other characters. The filename may then be entered.

The user may select either Binary [B] or Intel Hex [H] format to write the data.

When writing the buffer to disk, the number of bytes written corresponds to the size of the currently selected address range.

In case a file with the same name exists, the user will be prompted to confirm erasure of the previous file.

## PROM ERROR MESSAGES

The following is a list of common error messages for the PROM utility.

### 1) Disk Full, no data written.

The disk drive used for the write operation was too full to contain the entire file. The partially written file has been erased.

### 2) PROM not blank

The PROM contains data. The data in the SPRINT memory buffer cannot be over-programmed into the device.

### 3) O.K. to program on top of existing pattern?

PROM was not blank, the new pattern can be over-programmed onto the existing pattern. Enter 'Y' to commence programming.

### 4) Skip blank check?

Device is not blank. Enter 'Y' to program anyway.

### 5) Incompatible TOP POD

The currently installed TOP cannot support the operation attempted.

### 6) Manufacturer xx Device yy not recognized

Auto ID could not identify the device in the socket. Either the device does not support silicon signature, or the switch settings (**SPRINT<sup>plus</sup>** only) were not correct for the size of the device.

## PROM NOTES

1. Registered PROMs which have a programmable initialization byte, have this byte stored after the last data byte. The location in memory of this byte is demonstrated by these examples:

| Device size | Type         | initialize byte location (HEX) |

|-------------|--------------|--------------------------------|

| 1024        | 7c235, 27S35 | 400                            |

| 2048        | 7c245, 27S45 | 800                            |

| 8192        | 7c268, 7c269 | 2000                           |

SPRINT automatically programs this data into the PROM during the programming cycle. The byte can be read in from a device or from a disk data file. When reading a device, SPRINT automatically determines the reset byte value.

2. Proms which have additional programmable features have the data stored in a control byte after the reset byte value. For example :

| Device size | Type         | Control byte location (HEX) |

|-------------|--------------|-----------------------------|

| 2048        | 7c245, 27S45 | 801                         |

| 8192        | 7c268, 7c269 | 2001                        |

SPRINT automatically programs this data into the PROM during the programming cycle. The byte can be read in from a device or from a disk data file. When reading a device, SPRINT automatically determines the control byte value.

3. Microcontroller programming is identical to PROM programming, except that an additional byte contains a flag for the security fuse. This byte is located after the last data byte. If a device contains multiple fuses, the first fuse will be bit 0, the second bit 1, etc. Many microcontrollers require adapters (see Chapter 3 for adapter information).

4. (SPRINT<sup>plus</sup> only) When programming bipolar 16 and 18 pin PROMS, Vcc is supplied to these devices from the socket pin marked '<-20'. This means that either a jumper is required to connect this '20' pin to the device Vcc pin, or an intermediate socket can be inserted to make this connection.

5. The Cypress 7c245, 7c268 and 7c269 have programmable Enable and programmable SYNC bits. The control byte location contains the instructions for SPRINT for programming these extra features. The data stored in this location has the following meaning, a value of:

|                      |                 |

|----------------------|-----------------|

| 0 = async enable     | 7c245, 268, 269 |

| 1 = sync enable      | 7c245, 268, 269 |

| 2 = async initialize | 7c269           |

6. EEPROM. The Xicor 28C256 has 1 extra byte as security fuse. If this byte equals 1, the write protect feature of this device will be set after programming.

## M MANUAL PRODUCTION PROGRAMMING

IN **SPRINTplus**, and **SPRINT EXPERT** installations with a single pod installed, this command sets up a counter for programming a fixed number of devices. After entering the number of devices to program, the operator need only insert the device, and type any key to program. Programming stops after the unit count is reached.

In **SPRINT EXPERT DUAL** systems, the counter is first initialized, afterwards the active socket switches from right to left (SWAP mode). The currently active socket is shown by the LED pulsing. In this mode, one device can be programmed while the other socket is being loaded/unloaded. The operator need only type <space> to continue programming until the unit count is reached. This mode can double programming throughput.

The <ESC> key will turn off manual production mode. Failing devices are not counted.

## T. GANG / SET PROGRAMMING OPTIONS

This command is enabled if either a MultiSyste system is detected at power-on, or if a TOP432 is detected.

The default condition when starting **SPRINT EXPERT** MultiSyste systems is for the right-most socket to be enabled. This socket can be used in the same manual as a single **SPRINT** socket system.

The T command allows other options to be selected. The T command sub-menu contains the following options:

|    |                                   |           |

|----|-----------------------------------|-----------|

| N  | standard single mode operation    | (default) |

| G  | Gang mode operation               |           |

| E  | Eight bit set mode operation      | (TOP432)  |

| S  | Sixteen bit set mode operation    | (TOP432)  |

| T  | Thirty two bit set mode operation | (TOP432)  |

| L  | Switch to the right (left) socket | (DUAL)    |

| Ln | Select socket number 'n'          | (QUAD +)  |

**N:** Normal mode sets the system to the right most unit.

**G:** GANG mode, all sockets receive the same information, and all must be the same type. Set programming is only possible with the TOP432. In TOP432 mode - set programming can be done up to 32 bits (one TOP432). Multiple TOP432s can be used in GANG/SET mode, where multiple sets of EPROMs are programmed - each TOP432 unit receives the same information.

**E:** The 8 bit set mode places sequential data into each EPROM, 'stacking' the EPROMs together to hold the entire data loaded into memory.

**S:** The 16 bit set mode puts all odd data into the sockets 1 and 3, and even data into sockets 0 and 2. Two sets of 16 bit wide data can be programmed at a time.

**T:** The 32 bit set mode puts the 0th, 4th, 8th byte (etc) into socket 0, the 1st, 5th, 9th byte (etc) into socket 1, and so on.

**L:** As of the units can be directly and uniquely selected with this command. The change to a different TOP will cause PROM to enter the device menu, which will show the devices possible with that TOP. This mode of operation allows a DUAL or QUAD system to have different types of TOPs - one in each position.

**NOTE:** The SET or GANG mode must be selected before data is read into memory, because set modes and 4 megabit EPROMs requires 2 Megabytes of data - all of which is organized in the overlay data files for high-speed programming and efficient memory use.

**ERRORS:** Any errors detected during verify or programming will cause the LED of the socket with the error condition to turn RED. This RED LED will remain on after the programming cycle is complete. Other devices will continue to program.

## 2. SPRINT PLD FUNCTIONS

### STARTING PLD

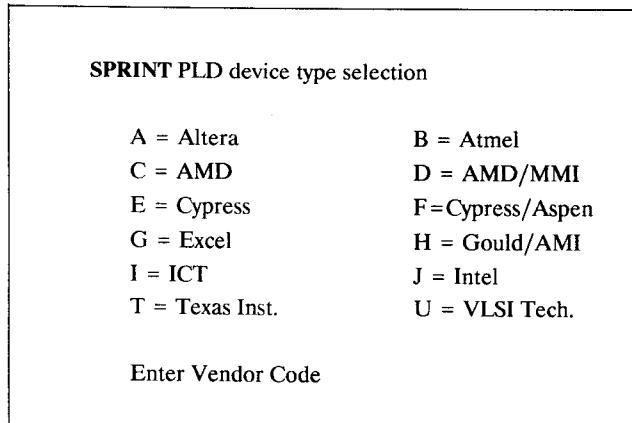

After entering the PLD programming utility, a menu of PLD manufacturers and vendors will appear on the screen. Next to each vendor in the menu is a single letter vendor code as shown below.

The user is then prompted for the vendor of the device that is to be programmed. The user should then type the single letter vendor code corresponding to the vendor of the device to be programmed. For example, entering a 'E' following this prompt would select Cypress, a 'D' would select MMI etc.

The user may also optionally make a print-out of all the supported devices for the version of the PAL utility that is being used. This is done by typing a '\*' instead of the vendor code. The list can be directed to the disk by pressing the '+' key. Some devices may have been added since your warranty or SMP period expired. These are listed in the printouts with a '+', and on the screen as SMP. Please contact your SPRINT distributor for an update.

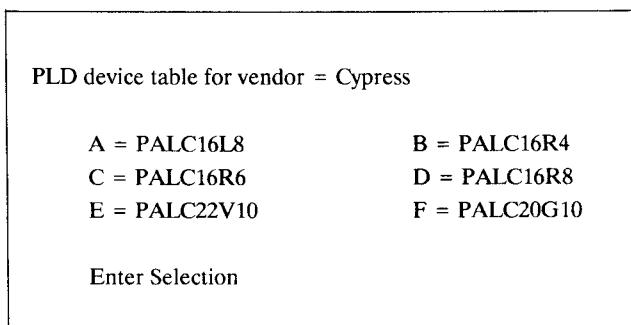

After the selection of the vendor is complete, a second menu will appear on the screen. This menu lists all the devices from the selected vendor that are currently supported by the SPRINT PLD programming utility. This menu also has a single key code for each device supported. The device to be programmed should be selected in the same way as the vendor was selected in the previous menu. For example, if Cypress was the selected Vendor and the device to be programmed was a PALC22V10, the user would have typed 'C' for Cypress in the first menu and 'E' for PALC22V10 in response to the second menu. Following is an example of a reduced device table as it would appear on the screen:

For some vendors (e.g. MMI) there are too many devices to display on a single menu. For these vendors a separate menu will appear which requests the user to choose a category of devices into which the device to be programmed falls (e.g. A-PALs, B-PALs etc.)

Incorrect selections are ignored. The size of the memory buffer is automatically set to the device size selected. Changing between compatible devices will not erase the data stored in memory. If a device type is changed to another device having an internal organization different from the initial device, the memory is reset to the blank condition in order to avoid operator errors.

PLDs have different internal sizes. Only valid fuse locations are enabled when a PLD type is selected. The internal size is compatible with the JEDEC data files generated by all PLD development software.

The user may at any stage during the device and vendor selection phase exit the PLD programming utility by hitting the Escape (ESC) key. This will return operation to the previous menu.

## MAIN MENU

Following the device selection, the main PLD programming utility menu is displayed on the screen. This menu is composed of a list of commands. Command selection is performed with a single key stroke (the single code letter corresponding to the command in the menu). Commands may be selected with either upper case or lower case letters, **SPRINT** will understand both. The function of each command is described in the following paragraphs of this Chapter. In the top right-hand corner of the screen the vendor and device that has been chosen are displayed. If this does not correspond to the vendor or the device that is to be programmed, then the user may change the device type and the vendor by executing command 'C' (Change device type), see below.

## MORE ? ERROR DISPLAY

If an error occurs during Blank Check, Verify, or Test, the user will be prompted with the message 'ERROR - display detailed report? [N]'. Entering any key except 'Y' will cause the main menu to be displayed with the 'FAIL' box blinking in inverse video. If the error display continues over 20 lines, the message 'MORE ? [N]' will be displayed, enter 'y' to continue, any other key to exit.

For blank check and verify errors, the detailed report will be an X-plot of the device with 'X' and '-' indicating the locations where incorrect data was read. Only erroneous locations will be displayed. The displayed 'X' or '-' is the data **SPRINT** expected to read from the device - the actual device therefore has the opposite data.

For test errors, either during a programming cycle or from the main menu 'T' command, the user will have the error displayed on the screen, and will be prompted to either display more errors, or exit. If SMP is installed, it is possible to enter the Test Vector Editor directly from the error screen. In the SMP test vector editor, the user need only type 'space' to have the failing test vector location graphically displayed on the screen.

## PLD PROGRAMMING COMMANDS

### A ASSEMBLE

The **SPRINT** PLD programming utility has a PLD macro-assembler included. This assembler is designed to convert PLDASM source files (ASCII text) into JEDEC compatible files that are needed to program the PLD itself. Details on the format of the PLDASM source files and the functions and operation of the assembler can be found in Chapter 4 of this manual.

The Assemble command loads the **SPRINT** PLD macro-assembler. The user is then presented with a list of all the files in the default directory with the default file extension (\*.PLD unless otherwise specified). The source file is then selected. The source file may be selected from the list presented on the screen or any other filename may be entered, specifying filename, directory and file extension. The assembler will generate a JEDEC standard compatible file with the same name as the source file but with a JED file extension in the same directory as the source file.

After assembly is complete, the system will return to the **SPRINT** main menu, the user should check that the desired device type is selected, and read in the file from the disk using the 'T' input command.

### B BLANK CHECK

This command verifies that the non-erasable device in the socket is empty. The device in the socket is read and the contents compared to the expected 'erased' condition. The device type selected must match the physical device inserted in the socket.

Electrically erasable devices do not require a blank check operation. These devices are automatically erased as part of the programming cycle.

The user has the option to display an XPLOT of those fuses that are not blank - as described in the Section on MORE ?.

## C CHANGE DEVICE TYPE

The currently active device type can be changed using this command. The user is prompted by a menu with the list of currently supported vendors and devices as is described in the introduction to this Chapter. After re-selection, **SPRINT** returns to the main menu.

The selection sequence is as follows. The vendor name is first selected using the single key code for each vendor, as shown on the menu screen.

Then the family code is selected. The family code is typically shown on the physical device before and after the device type. For example, the family type for an AMD AmPAL16L8A is AmPAL--A. For a Texas Instruments TIBPAL16L8-10, the family code is TIBPAL -- 10.

Finally the actual device type (architecture) is selected. A little practice with selecting device types will show that this is the quickest and easiest method for selecting a device. It may be useful to print out a directory of device types with the '\*' or '+' options until you are familiar with the approach.

**SPRINT** does not list package options, since package options do not affect the programming algorithm of the device. When using SMD devices, simply select the same device name as for the DIP device.

To allow copying from one device type to another, memory contents are not erased when changing between devices with the same architecture. The device type selected is shown on the main menu screen. If, when changing device types the internal size of the fuse arrays changes, the memory will be reset to the blank condition (checksum = 0) to avoid incorrect conversions.

**SPRINT<sup>plus</sup>** users must check the filter switch settings before reading or programming any device.

**NOTE: Reading and programming PLDs involves the use of voltages higher than 5V. If the device type displayed on the main menu is not the same as the device in the socket, damage to the device may result.**

## CROSS PROGRAMMING

Cross programming is a feature provided to support many 16V8, 20V8 and related devices. The idea of cross programming is that the programmer accepts a first generation device type (for example 12H6) and programs a JEDEC file for that device directly into a replacement device (the 16V8). The JEDEC map of the 12H6 is not compatible to the 16V8, therefore the programmer must do the translation at the moment when the 16V8 is to be programmed. **SPRINT** supports 42 different first generation devices, and presently 2 different replacement devices (16V8 and 20V8). To use cross programming, simply select the replacement device with the 'AS' option. For example '16V8 as'. Then select the first generation device from the '16V8 as' menu (12H6). You can now read in the 12H6 JEDEC file and program the 16V8. All architecture bits and signature fields will be automatically configured. No translation is required.

In order to support devices that are too complex for direct cross programming, the **SPRINT** PLD programming utility supports a conversion via the 'X' command. The 'X' command is explained below. Most popular PAL and EPLD types can be converted with this tool. (SMP is required).

## D DOS COMMAND

This allows MSDOS commands to be executed without leaving the **SPRINT** environment. If the file 'COMMAND.COM' is not located in the current directory, or cannot be found via the PATH, then the function will not work. Any normal DOS command can be entered, in the same manner as in DOS itself. For example:

DIR \*.JED

will list all the files with the extension or file type ".JED" (often used for JEDEC format files). You can return to PAL operation by typing 'EXIT'.

## E EDIT MEMORY CONTENTS

**SPRINT** includes a very powerful editor to help you to understand the internal configuration of a PAL or EPLD. The display includes identification of the pin numbers associated with the various product terms, and displays the internal features with the node numbers corresponding to popular PLD compilers. The editor can be used to debug PAL designs, or to verify the output of assemblers or compilers. Any fuse in the device can be changed. It is recommended that 'snow' be exercised to set the fast mode (see 'snow' description). The faster screen updating is useful both for EDIT and for the test vector editor. We refer to the programmable elements of the device as 'fuses' even if they may be erasable CMOS cells.

**NOTE: The modification of PLDASM source files and reassembling of that source is a more practical method for making modifications to a PAL's equations and is less likely to result in errors.**

After entering 'E' for Edit, the user sees a display of the X PLOT on the screen. By using the cursor keys, any fuse can be pointed to and changed if desired. For popular PAL and EPLD devices, the pin numbers corresponding to the product terms shown on the screen are displayed. Internal Set and Reset terms are displayed as SP and AR respectively. Device Architecture bits are displayed as 'A'. Other nodes internally are displayed as N1, N2 etc.

## EDIT (continued)

The program then waits for user commands as follows:

|           |                                                            |

|-----------|------------------------------------------------------------|

| home      | goes to fuse 0                                             |

| end       | goes to first fuse, last product term or architecture row. |

| page up   | 24 lines up                                                |

| page down | 24 line down                                               |

| arrows    | moves cursor one location                                  |

| ^left     | control left moves to left margin                          |

| ^right    | control right moves to right margin                        |

| <cr>      | display next line                                          |

| Backspace | moves cursor one location left                             |

| <esc>     | exit to main program                                       |

| X         | stores a 0, meaning 'connect' at the current fuse          |

| -         | stores a 1, meaning 'disconnect' at the current fuse       |

| 1         | set entire product term to no connect (on)                 |

| 0         | set entire product term to all connected (off)             |

| *         | print the XPLOT on the printer                             |

| F1        | display help screen                                        |

| F2        | do not display product terms that are off, (all '0')       |

| F3        | toggle screen mode - fast/slow                             |

| F4        | display JEDEC fuse numbers/display product term numbers    |

After exiting, the new checksum of memory is calculated and displayed on the main menu screen. Any change in the checksum will cause the filename display to be reset.

'Snow' is an affliction of many older CGA and MDA screens. Depending on the type of the display controller, white specks could be seen on the screen whenever the computer wrote data to the screen display. Setting 'snow' to slow mode turns off the white specks, at the expense of speed. Modern controllers do not have this problem. The default condition is fast.

## G EXERCISE DEVICE (EDIT TEST VECTORS)

This function is available as an additional SMP option. Contact your **SPRINT** distributor for information about this feature if your present system does not display the 'G' command in the main menu.

Please read the Section on the 'T' function for more information about test vectors and related problems.

This function is invoked in one of two ways. The 'G' command from the main menu will start the exercise directly. This is the method an engineer would use to develop and test a suite of test vectors. The 'G' command offers a graphic display of the device in the socket, and allows interactive development of PAL/EPLD vector test functions. Once a suite of vectors has been generated, they can be stored on the disk with the normal 'W' command - they will be attached to the JEDEC fuse description file. The UNASM program can also be used to create a transportable source file of the test vectors.

The second method is to optionally enter the exercise mode if the device in the socket fails the test vectors loaded into memory as part of the standard JEDEC file. If an error occurs, either as part of the normal programming cycle or from the main menu 'T' command, the user will be prompted with the option to 'enter test/edit mode'. In the production programming environment, the operator would enter 'N', and the menu will report 'FAIL'. In the laboratory, entering 'Y' to enter EXERCISE followed by 'SPACE' to run the vectors, will cause the failing location to be displayed on the screen, the failing bits are shown in red (or inverse video in monochrome systems).

One purpose of this function is to allow a device failing a vector test to be examined. The exerciser will display in red those pins which do not match the expected result. After starting the function, entering 'SPACE' will step through the vectors in memory until an error (or the end) is reached. The 16 vectors prior to the stopping point, the current vector and the next 3 vectors will be displayed on the screen. The engineer can examine the error, change input conditions, or expected output levels, single step through the cycles and determine whether the error is due to the test vector or an actual failing device.

Another purpose is to develop test vectors for a device. This could be done as part of the design cycle. Using the exerciser, a programmed PAL in the socket can be stimulated with all input conditions and the result can be seen directly on the screen. The test vectors created in this manner can be then stored on the disk for use in testing production devices. If the device does not behave as expected, then the source file for the device can be changed until the device functions as expected.

Exercise (continued)..

The exerciser could also be used to apply signals to any device in the socket to observe the results, standard 74 series TTL, HC cmos, PROMs, or any other product can be examined in this manner. To allow any type of devices to be tested, the select menu includes the device type 'Test a chip with xx pins'. Note that Vcc drivers are available on certain pins of the socket, refer to Chapter 3 for the VCC driver list for the POD you are using.

## STARTING EXERCISE

When this command is started, an image of the device in the socket is displayed on the screen. All pins are set to the level '?'. The level/function menu is displayed, and, if test vectors are in memory, the first 4 will be displayed. To execute the vectors in memory, the 'E', 'G', 'R', or 'SPACE' functions may be entered.