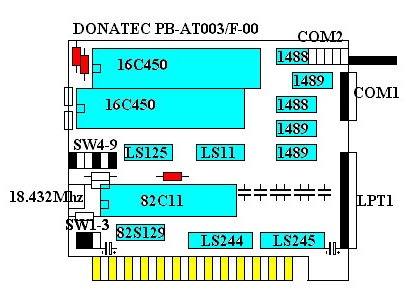

DONATEC Serial RS-232 and parallel Port ISA Card

AT parallel / Serial Adapter FT 8608030

V4.1

resources page

Carte port parallèle et série bus ISA DONATEC

COMMUNICATION PORTS

![]()

This card provides a parallel

port configured as LPT1 or LPT2 and serial communication ports configured

as COM1 and COM2.

Port 1 COM1 address 3F8-3FFH IRQ4

Port 2 COM2 address 2F8-2FFH IRQ3

Parallel Printer Port LPT1 0378:037FH IRQ7

The purpose is to understand how the PROM 82S129 is used in this design.

Before the advent of programmable logic, PROMs were often used in lieu of discrete logic.

I expect that PROM was used to decode particular ISA bus addresses and perhaps other ISA bus signals and react accordingly.

In other words, certain locations in the PROM would be programmed to react so that the output pins would be in the right state for a particular address.

That particular PROM has 8 address inputs and four outputs.

Here is an example of how you would use a PROM as logic. Let's say you wanted

to make a 3 input NAND gate. For discuss purposes we will use the upper

three bits of the address lines as inputs and one of the 8 data output bits

as the NAND output. The programming of the PROM would be as such:

All PROM locations from 00000000 to 00011111 would have a data output pattern

of 1111 (assuming the default output state of the PROM is a '1').

For all PROM locations from 11100000 to 1111111 would have a data output

of 0111 (assuming the default output state of the PROM is a '1').

With this programming, any time the upper three address bits are a '1',

then Bit 0 of the data output bits will be a '0', which is a 3 input NAND

function.

As you can imagine, figuring out which addresses should have particular

data output patterns can get quite complicated when you use a PROM as a

replacement for random logic.

Another issue with using PROMs for logic replacement is that their outputs

are glitchy, meaning, when one input pin changes you can have momentary

glitches on any or all of the outputs while the internal address decoder

of the PROM settles. Because of this behavior, PROMs were often used in

a synchronous fashion to avoid the glitches. Programmable Logic does not

have this issue which is why it is so popular.

Here is the diagram of the card (in progress)

![]() The

content of the bipolar PROM 82S129 "FAT03011D" is given here :

82S129.BIN

The

content of the bipolar PROM 82S129 "FAT03011D" is given here :

82S129.BIN

![]() dump of the bipolar PROM 82S129.TXT

dump of the bipolar PROM 82S129.TXT

![]() Adaptateur

parallèle série DONATEC 286-12 Guide de l'utilisateur

(PDF-18 pages - 443 Kb)

Adaptateur

parallèle série DONATEC 286-12 Guide de l'utilisateur

(PDF-18 pages - 443 Kb)

![]() Datasheet

of the PROM 82S129 1K-Bit

TTL Bipolar PROM (256 x 4)

Datasheet

of the PROM 82S129 1K-Bit

TTL Bipolar PROM (256 x 4)

![]() Datasheet

of the UM82C11 PRINTER ADAPTER

INTERFACE (PAI)

Datasheet

of the UM82C11 PRINTER ADAPTER

INTERFACE (PAI)

![]() Datasheet

of the UART NS16C450N UNIVERSAL

ASYNCHRONOUS RECEIVER/TRANSMITTER (UART),

Datasheet

of the UART NS16C450N UNIVERSAL

ASYNCHRONOUS RECEIVER/TRANSMITTER (UART),

![]() Notice

de la carte mère DONATEC 286 (1.48Mb - 27 pages) This brochure

details the connexions of the ISA Bus (See page 12 to 19)

Notice

de la carte mère DONATEC 286 (1.48Mb - 27 pages) This brochure

details the connexions of the ISA Bus (See page 12 to 19)

![]() Notice de la carte RS-232/IMPRIMANTE

pour PC/AT DONATEC Réf. IF201 DONATEC (906Kb - 7 pages)

Notice de la carte RS-232/IMPRIMANTE

pour PC/AT DONATEC Réf. IF201 DONATEC (906Kb - 7 pages)

![]() KMA-202F-12R

PC-AT286 Motherboard User's Manual (PDF - 920Kb- 50 pages)

KMA-202F-12R

PC-AT286 Motherboard User's Manual (PDF - 920Kb- 50 pages)

******

![]()

Important Notice: Also if you have any data about this kind of interface, do not hesitate to contribute to this page.

Retour au sommaire

Retour au sommaire Retour

à la Page d'accueil

Retour

à la Page d'accueil matthieu.benoit@free.fr

matthieu.benoit@free.fr